# Integration of Si/Si-Ge nanostructures in micro-thermoelectric generators

**Gerard Gadea**

Aquesta tesi doctoral està subjecta a la llicència <u>Reconeixement 3.0. Espanya de Creative</u> <u>Commons</u>.

Esta tesis doctoral está sujeta a la licencia <u>Reconocimiento 3.0. España de Creative</u> <u>Commons.</u>

This doctoral thesis is licensed under the **Creative Commons Attribution 3.0. Spain License**.

### **Integration of Si/Si-Ge nanostructures**

### in micro-thermoelectric generators

#### Thesis by

Gerard Gadea

In partial fulfilment of the requierements for the Degree of Doctor of Philosophy

Supervisors:

Albert Tarancón and Álex Morata

Tutor:

Francesca Peiró

Department of Electronics

University of Barcelona

Doctorado en Nanociencias - Universidad de Barcelona - 2017

## Acknowledgements

I'm grateful to many people – family, friends, colleagues, cats – but specially to Albert Tarancón, Álex Morata, Jose Domingo Santos and Mercè Pacios, who made possible this journey. Thank you very much, for real!

### Resumen

Los materiales termoeléctricos permiten la conversión de calor a electricidad y viceversa. Esto permite explotar el efecto termoeléctrico en generadores termoeléctricos, capaces de extraer energía térmica de fuentes calientes y convertirla a electricidad útil. Estos generadores presentan grandes ventajas, como su falta de piezas móviles — y por ende necesidad de mantenimiento alguna — y su total escalabilidad, que permite cambiar su tamaño sin afectar su rendimiento. Esto los hace obvios candidatos para la alimentación y carga de dispositivos portátiles y situados lugares de difícil acceso. A pesar de ello, su uso no está muy extendido debido a que su relación eficiencia-coste es baja en comparación a otros métodos capaces de suplir las funciones de alimentación — como la sustitución periódica de baterías — o de conversión térmica-eléctrica — como las turbinas de vapor. Los materiales termoeléctricos suelen ser o eficientes y caros (como el Bi<sub>2</sub>Te<sub>3</sub> usado en los módulos comerciales) o ineficientes y de bajo coste (como el silicio, barato por su abundancia ya que supone un 28% de la corteza terrestre).

En este trabajo se han crecido nanostructuras de silicio y silicio-germano, con dimensiones en el orden de los 100 nm. Los nanomateriales presentan propiedades termoeléctricas mejoradas respecto a sus contrapartes macroscópicas. Gracias a la nanoestructuración pues, se ha abordado del problema de eficiencia-coste por dos vertientes:

- En el caso del silicio normalmente un mal termoeléctrico debido a su alta conductividad térmica se ha habilitado su uso como termoeléctrico al crecerlo en forma de nanohilos cristalinos y nanotubos de silicio policristalino.

- En el caso de silicio-germano que ya es un buen termoeléctrico para uso en altas temperaturas – se ha aumentado su eficiencia aún más, creciéndolo en forma de nanohilos.

Yendo más allá de la síntesis, los nanohilos de silicio/silicio-germano se han optimizado, caracterizado en integrado en gran número micro-generadores termoeléctricos de 1 mm² de superficie, pensados para la alimentación de pequeños dispositivos y circuitos integrados. Respecto a los nanotubos de Si, estos se han obtenido en densas fibras macroscópicas aptas para su aplicación directa como generadores termoeléctricos de gran área. Cabe mencionar que ambos nanomateriales — así como los microgeneradores basados en nanohilos — fueron obtenidos mediante técnicas actualmente utilizadas para la fabricación de circuitos integrados, pensando en la escalabilidad del proceso para su aplicación.

El trabajo presentado en esta tesis consiste en el crecimiento, optimización, estudio e integración de nanostructuras de Si/Si-Ge para su aplicación en generación termoeléctrica. En los Capítulos 1 y 2 se pone un marco a los materiales tratados y su aplicación y se describen los métodos utilizados, respectivamente. Los resultados se han dividido en cuatro capítulos. En los Capítulos 3, 4 y 5 se tratan los nanohilos abordando su crecimiento, caracterización y aplicación en microgeneradores, respectivamente. En el Capítulo 6 se tratan las fibras de nanotubos, integrando todo el estudio en el mismo capítulo. Finalmente en el Capítulo 7 se muestran las conclusiones, resumiendo los resultados e indicando la relevancia del trabajo.

### **Summary of results**

Silicon and silicon-germanium nanostructures were grown, integrated, optimized and characterized for their application in thermoelectric generation. Specifically two kinds of nanostructures were worked: silicon and silicon-germanium nanowire arrays (Si/Si-Ge NW) and polycrystalline silicon nanotube fabrics (pSi NT).

The results are dived in four chapters. Chapters 3, 4 and 5 deal with Si/Si-Ge NWs, while chapter 6 presents the pSi NT fabrics.

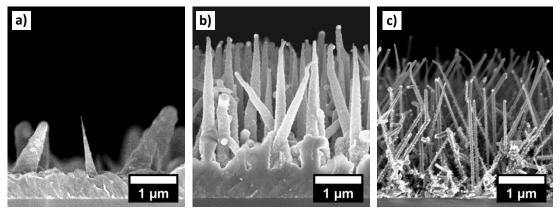

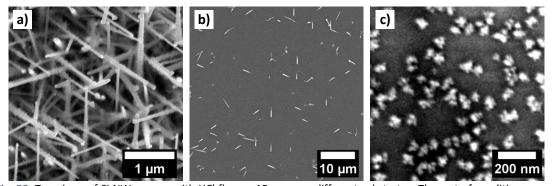

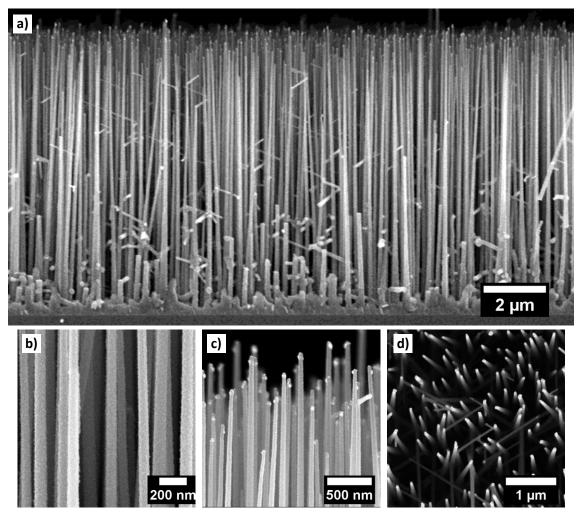

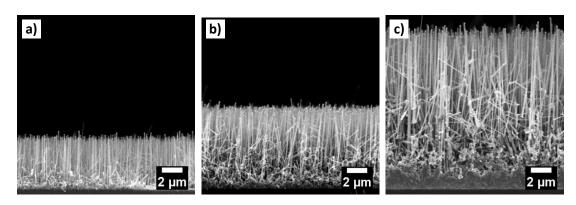

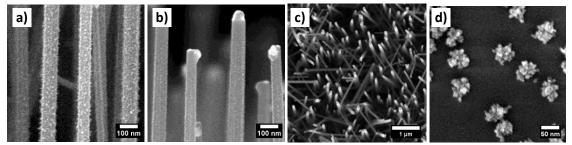

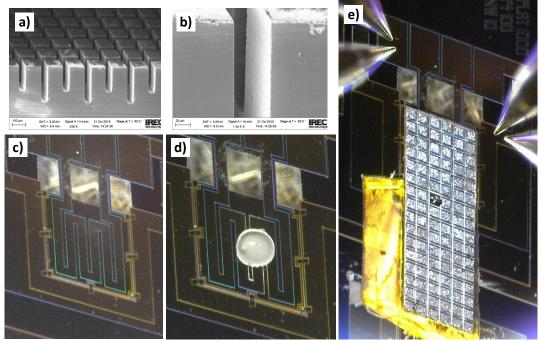

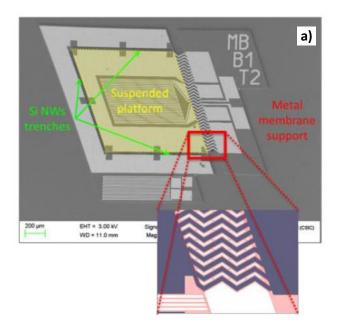

In Chapter 3 the growth and integration of Si/Si-Ge NWs was studied, in order to optimize their properties for thermoelectric application in micro-thermoelectric generators ( $\mu$ TEG). First, the methods for depositing gold nanoparticles prior to NW growth were studied. Second, the growth of NWs from the gold nanoparticles in a Chemical Vapour Deposition (CVD) process was comprehensively studied and optimized for subsequent integration of NWs in  $\mu$ TEGs, both of Si and Si-Ge. All important properties – NW length, diameter, density, doping and alignment – could be controlled by tuning the seeding gold nanoparticles and the process conditions, namely temperature, pressure, flows of reactants and growth time. Finally, integration was demonstrated in micro-structures for thermoelectric generation and characterization. The optimization process yielded to fully integrated thermoelectric Si/Si-Ge NW arrays with diameters and densities of ~100 nm and 5 NW/ $\mu$ m² respectively.

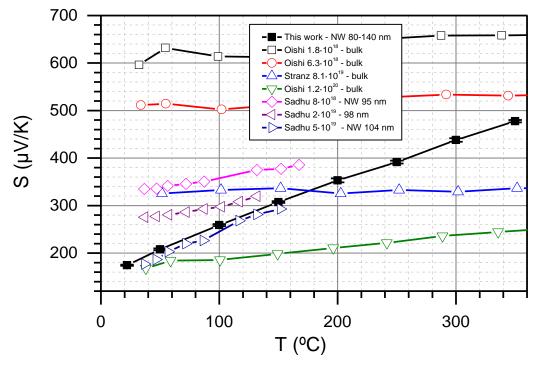

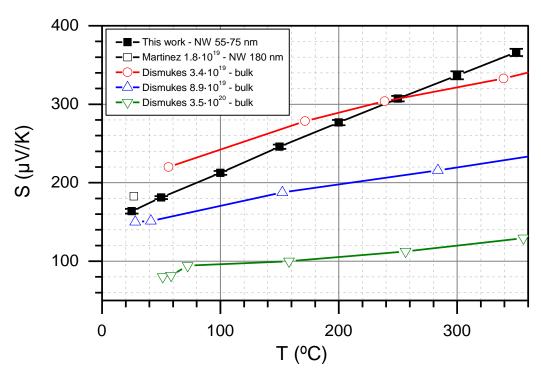

In Chapter 4 the Si NWs were thermoelectrically characterized. The Seebeck coefficient, electrical conductivity and thermal conductivity of arrays and single Si-NWs were measured in microstructures devoted to characterization comprising NWs integrated as in final  $\mu$ TEG application. Additionally a novel atomic force microscope based method for determination of thermal conductivity was explored. Then the results were discussed comparing them with existing literature. A ZT of 0.022 was found at room temperature, revealing an improvement of factor 2-3 with respect to bulk.

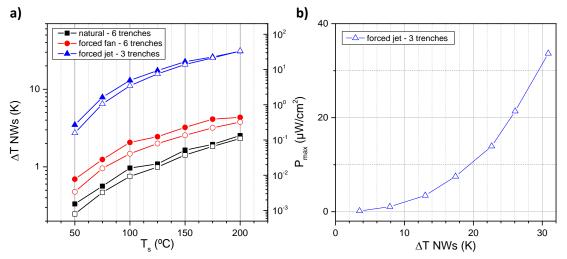

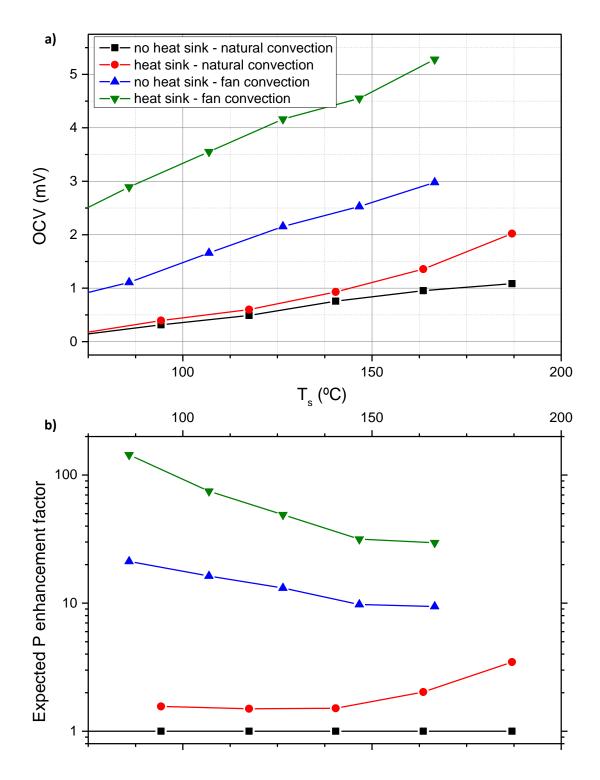

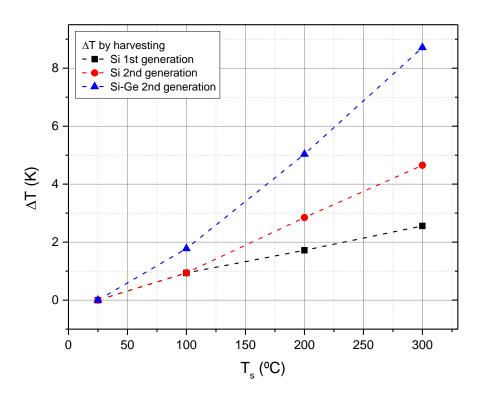

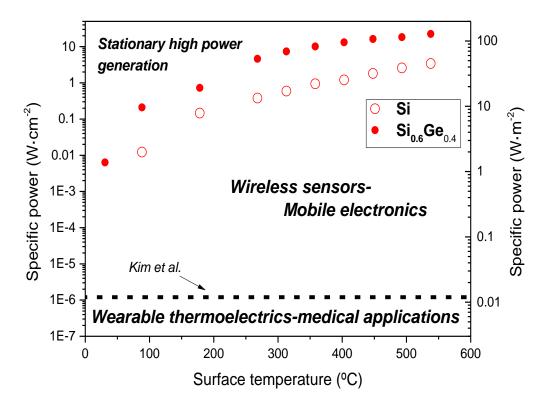

In Chapter 5 The harvesting capabilities of  $\mu$ TEGs with integrated Si/Si-Ge NWs was assessed. The thermal gradient and the power of the  $\mu$ TEGs was assessed for two generation of devices and for two thermoelectric materials, namely Si and Si-Ge NWs, which were integrated for the first time in functional generators. Also a study on heat sinking and convection effects was conducted adding insight towards further device improvement. Finally, the results were discussed and compared with literature. The maximum power densities attained were 4.5  $\mu$ W/cm² for the Si NWs and 4.9  $\mu$ W/cm² for the Si-Ge NWs while harvesting over surfaces at 350 °C.

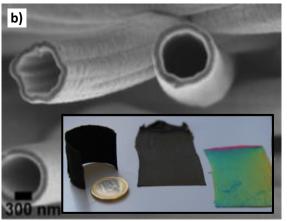

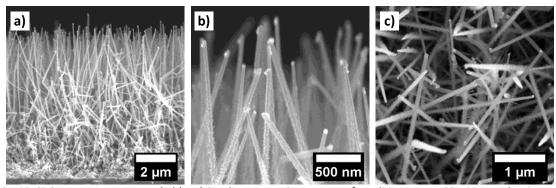

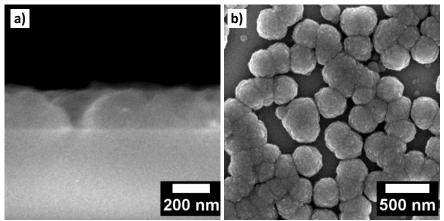

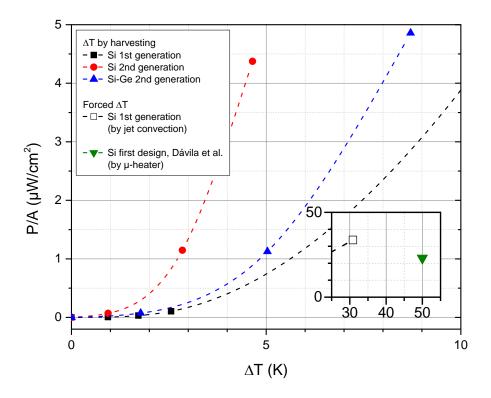

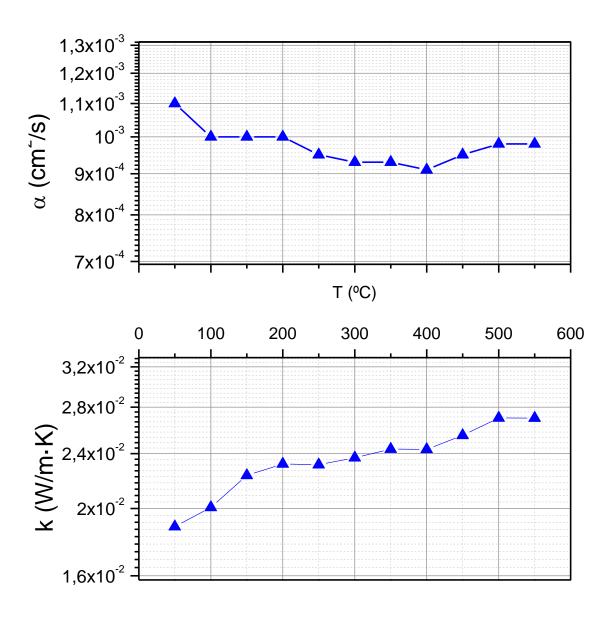

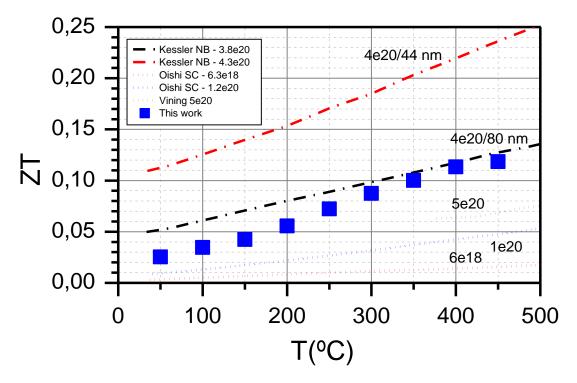

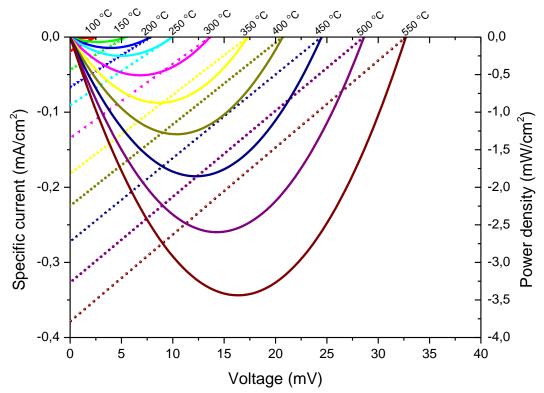

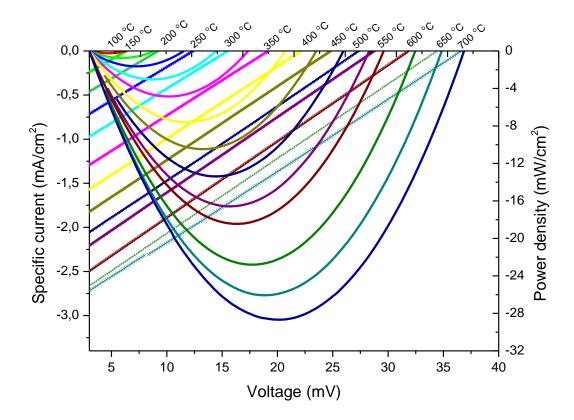

Chapter 6 deals with pSi NT fibers. First this new material concept and the growth route are presented, showing the fabrication steps and the control of the resulting properties by CVD method. Then the material is thermoelectrically characterized, by measuring its Seebeck coefficient and electrical and thermal conductivities up to 450 °C. A ZT of 0.12 was found, doubling the optimally doped bulk at this temperature. Finally a proof of concept was demonstrated by assessing the thermal harvesting capabilities of the material on top of hot surfaces. A maximum of 3.5 mW/cm² was attained at 650 °C.

### Scope of the thesis

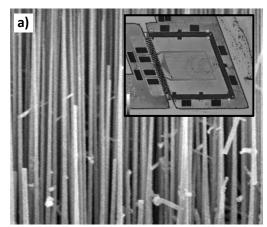

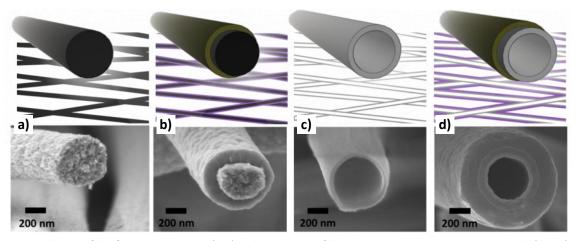

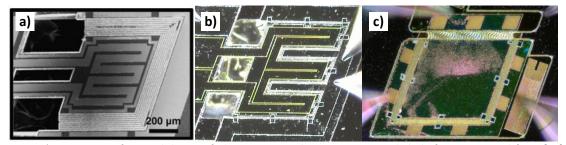

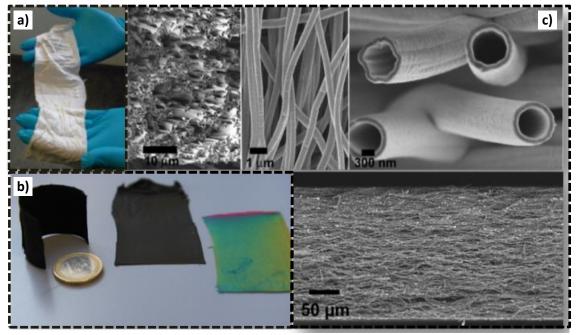

This thesis aims to grow, characterize and optimize silicon / silicon-germanium nanostructures for application in thermoelectric generation – i.e. in generation of electricity from a heat source by means of the Seebeck effect. Specifically, this work deals with two kinds of nanomaterials: i) crystalline nanowire arrays for micro-devices and ii) polysilicon nanotube fabrics for large scale application (Fig. 1).

Fig. 1. a) silicon-germanium nanowire array and micro thermoelectric generator ( $\mu$ TEG) in inset. b) polycrystalline silicon nanotubes and fabrics in inset.

The motivation of this work is, first, taking advantage of the positive effects of nanostructuration on thermoelectric properties of the materials under study, namely: i) increasing silicon-germanium thermoelectric efficiency and ii) rendering abundant and inexpensive silicon a thermoelectric material, otherwise ineffective. Second, optimizing these nanostructures, from growth to integration in devices, for their application in thermoelectric power generation. Finally, to characterize these nanostructures along the path, bringing new insight in nanomaterial thermoelectric properties / characterization techniques.

This thesis is organized as follows:

- **Chapter 1. Introduction.** The basics of thermoelectricity and the thermoelectric materials of interest Si/Si-Ge nanostructures are introduced in order to put a frame around the materials under study.

- Chapter 2. Experimental. The techniques used for of growth, integration and characterization of nanostructures are described. Also, the micromachined devices used for integration and characterization of nanowires are presented and described.

- Chapter 3. Si/Si-Ge nanowire array integration. The work regarding nanowire

growth optimization for thermoelectric application and device integration is

presented. First, the optimization and study of Si and Si-Ge NW growth methods

is presented. Then the results of this optimization are demonstrated by

integrating the NWs in micro thermoelectric generators/test structures.

- Chapter 4. Si nanowire thermoelectric characterization. The determination of thermoelectric properties of Si NWs is presented, along with discussion and comparison with other works. Also a novel thermal characterization technique based on atomic force microscopy is explored.

- Chapter 5. Si/Si-Ge nanowire based micro-thermoelectric generator. The applied results of the integration of NWs in thermoelectric micro-generators are presented, testing their power harvesting capabilities. Performances of different devices integrating Si/Si-Ge NWs are compared among them and with other existing µTEGs. Also device aspects as heat sinking and convection regimes are studied and discussed.

- Chapter 6. pSi nanotube fibers. The results on the growth, thermoelectric and harvesting characterization of a novel silicon based material scalable for large area thermoelectric application are presented.

- **Chapter 7. Conclusion** Summarizes the achievements attained in this work and their relevance.

### **Table of contents**

| Sc | ope of  | the th | hesis                                                     | 7  |

|----|---------|--------|-----------------------------------------------------------|----|

| Tá | able of | conte  | ents                                                      | 9  |

| 1. | Intro   | oduct  | tion                                                      | 13 |

|    | 1.1.    | Moti   | ivation                                                   | 13 |

|    | 1.2.    | Ther   | rmoelectric effect                                        | 14 |

|    | 1.3.    | Ther   | rmoelectric devices                                       | 16 |

|    | 1.3.    | 1.     | Applications of the thermoelectric effect                 | 16 |

|    | 1.3.    | 2.     | Thermoelectric device design                              | 17 |

|    | 1.3.    | 3.     | Device efficiency                                         | 18 |

|    | 1.4.    | Ther   | rmoelectric materials                                     | 21 |

|    | 1.4.    | 1.     | Materials for high ZT – intercorrelation of TE properties | 21 |

|    | 1.4.    | 2.     | Si/Si-Ge nanostructured materials                         | 23 |

| 2. | Expe    | erime  | ental                                                     | 27 |

|    | 2.1.    | Nand   | ostructure growth and integration                         | 27 |

|    | 2.1.    | 1.     | Chemical Vapour Deposition – technique and reactor        | 27 |

|    | 2.1.    | 2.     | VLS growth for Si/Si-Ge nanowires                         | 29 |

|    | 2.      | 1.2.1  | Growth mechanism and chosen precursors                    | 29 |

|    | 2.      | 1.2.2  | 2. Seeding methods                                        | 32 |

|    | 2.      | 1.2.3  | B. CVD-VLS growth and monolithic integration of NWs       | 37 |

|    | 2.1.3   | 3.     | VS growth for pSi nanotube fabrics                        | 39 |

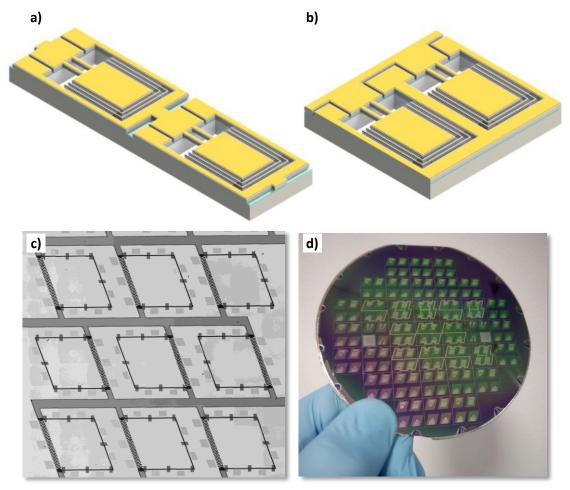

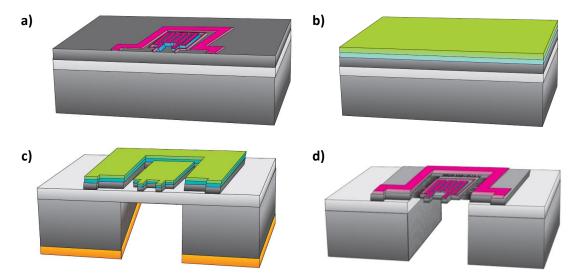

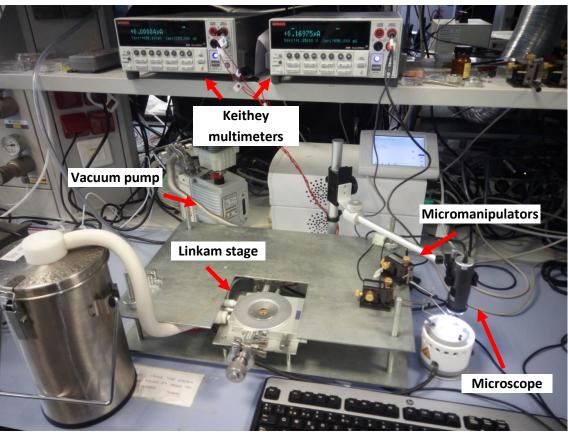

|    | 2.2.    | μΤΕΟ   | G devices for nanowire integration                        | 42 |

|    | 2.3.    | Mor    | phological/compositional characterization                 | 47 |

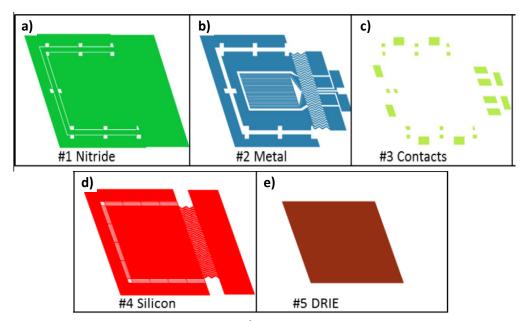

|    | 2.4.    | Ther   | rmoelectric characterization                              | 49 |

|    | 2.4.    | 1.     | Electrical measurements                                   | 49 |

|    | 2.4.    | 2.     | Si/Si-Ge NWs                                              | 50 |

|    | 2.      | 4.2.1  | Seebeck                                                   | 50 |

|    | 2.      | 4.2.2  | 2. Electrical conductivity                                | 53 |

|    | 2.      | 4.2.3  | 3. Thermal conductivity                                   | 55 |

|    | 2.      | 4.2.4  | I. Thermoelectric power harvesting (h                     | 57 |

|    | 2.4.    | 3.     | pSi NT fabrics                                            | 58 |

|    | 2.      | 4.3.1  | . Seebeck coefficient                                     | 58 |

|    | 2.      | 4.3.2  | 2. Electrical conductivity and thermoelectric harvesting  | 59 |

|    |      | 2.4.3.3      | 3.         | Thermal diffusivity and thermal conductivity    | 60  |

|----|------|--------------|------------|-------------------------------------------------|-----|

| 3. | Si   | i/Si-Ge I    | NW i       | ntegration in thermoelectric micro-devices      | 63  |

|    | 3.1. | Intro        | oduc       | tion                                            | 63  |

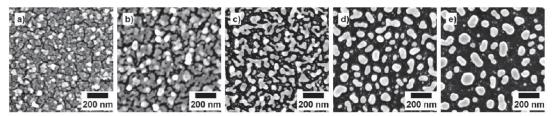

|    | 3.2. | Con          | trol c     | of Au seed nanoparticle deposition              | 64  |

|    | 3.   | .2.1.        | Coll       | oid deposition                                  | 64  |

|    | 3.   | .2.2.        | Galv       | vanic displacement                              | 66  |

|    |      | 3.2.2.1      | l.         | Au NP Size control                              | 66  |

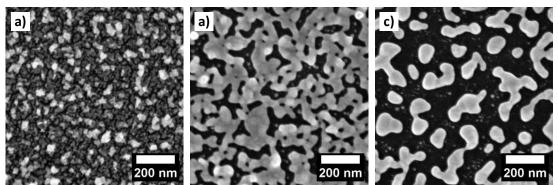

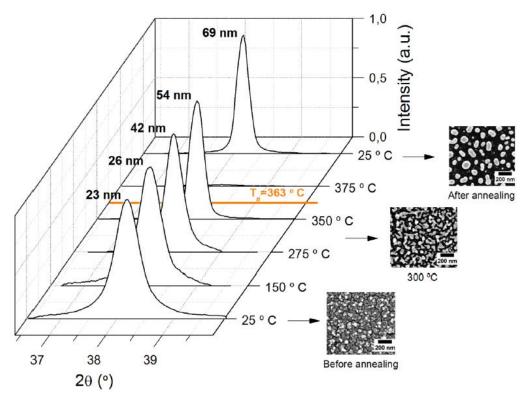

|    |      | 3.2.2.2      | 2.         | Au NP formation mechanism                       | 68  |

|    |      | 3.2.2.3      | 3.         | Au NP crystalinity                              | 71  |

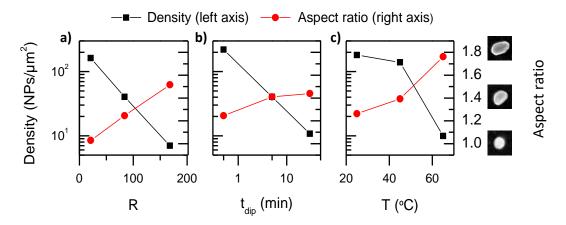

|    |      | 3.2.2.4      | 1.         | Au NP aspect ratio and density control          | 72  |

|    | 3.3. | Con          | trol c     | of CVD-VLS grown NW properties                  | 73  |

|    | 3.   | .3.1.        | Opt        | imization goals                                 | 73  |

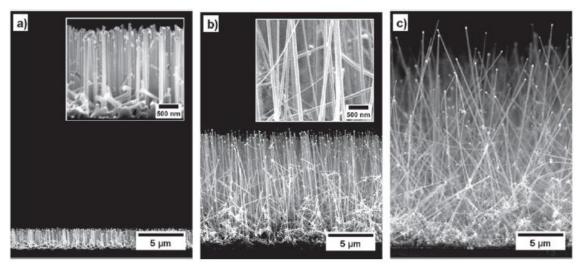

|    | 3.   | .3.2.        | Si N       | W growth                                        | 74  |

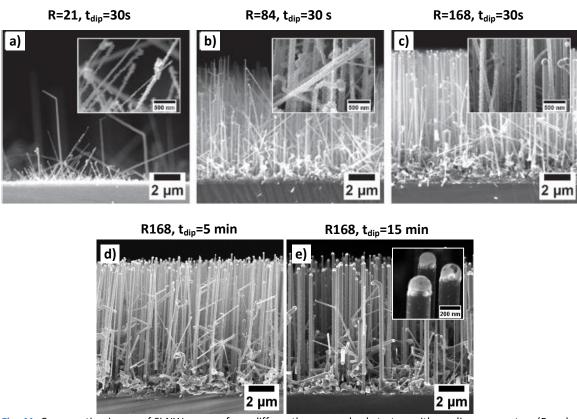

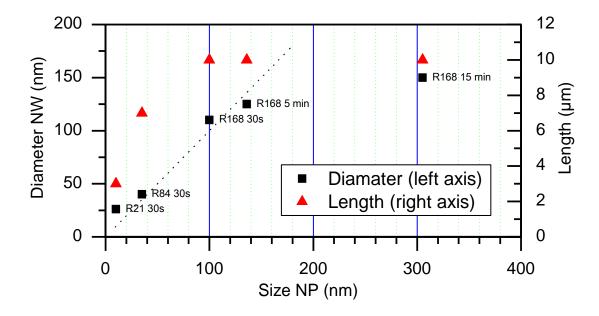

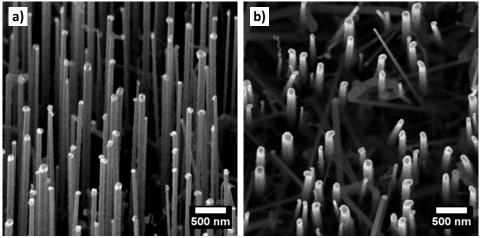

|    |      | 3.3.2.1      | l.         | Au NP seed effect                               | 74  |

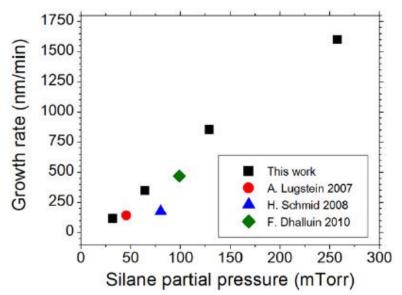

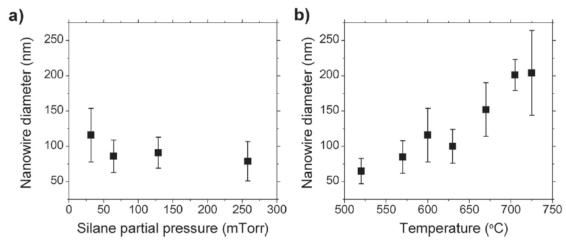

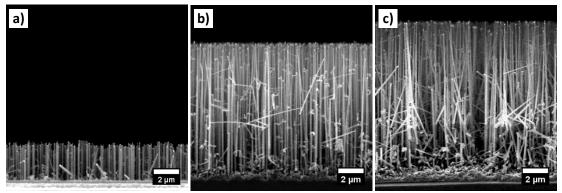

|    |      | 3.3.2.2      | 2.         | Growth pressure effect                          | 78  |

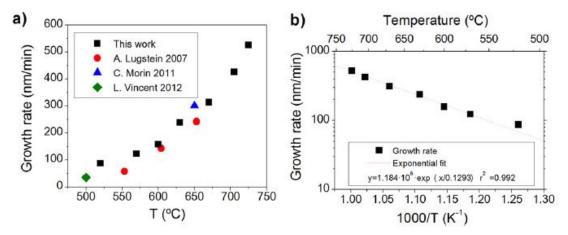

|    |      | 3.3.2.3      | 3.         | Growth temperature effect                       | 80  |

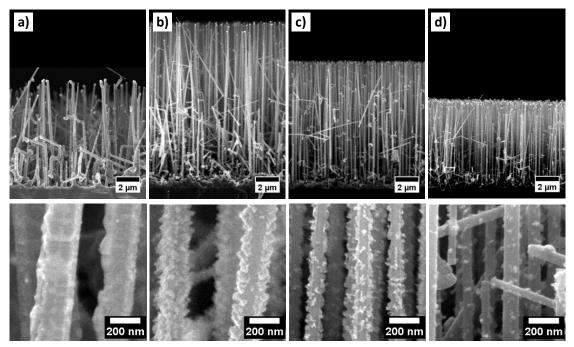

|    |      | 3.3.2.4      | 1.         | HCl effect                                      | 83  |

|    |      | 3.3.2.5      | 5.         | Origin of Si deposit near substrate             | 85  |

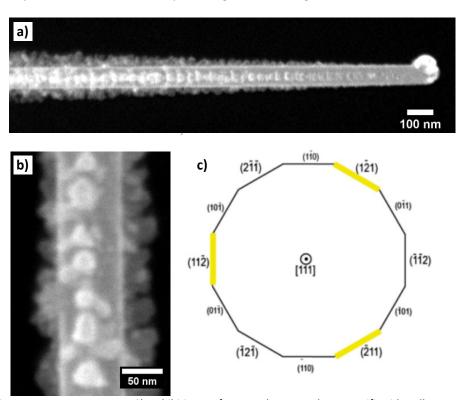

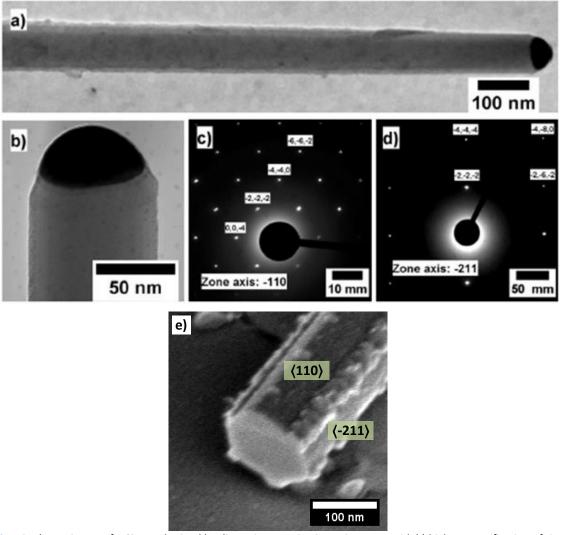

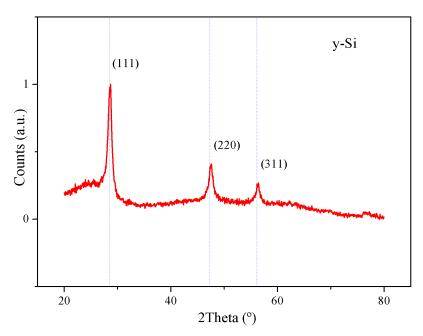

|    |      | 3.3.2.6      | <b>5</b> . | NW crystalinity assessment                      | 85  |

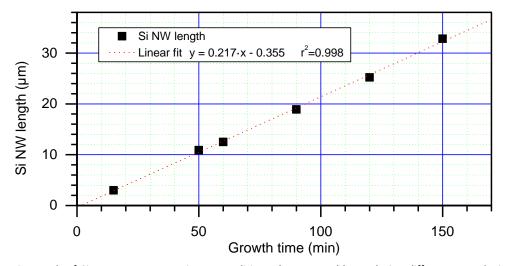

|    |      | 3.3.2.7      | 7.         | Optimum conditions and growth rate              | 87  |

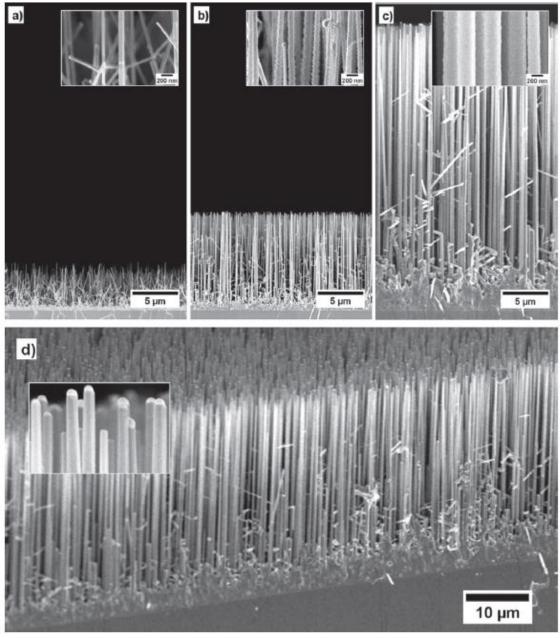

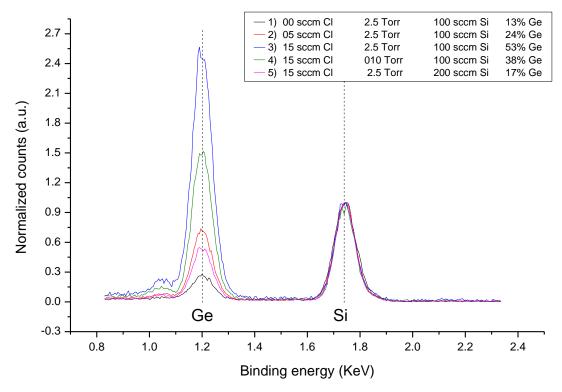

|    | 3.   | .3.3.        | Si-G       | e NW growth                                     | 90  |

|    |      | 3.3.3.1      | l.         | HCl effect                                      | 90  |

|    |      | 3.3.3.2      | 2.         | Pressure effect                                 | 93  |

|    |      | 3.3.3.3      | 3.         | SiH <sub>4</sub> -GeH <sub>4</sub> flows effect | 94  |

|    |      | 3.3.3.4      | 1.         | Optimum conditions and growth rate              | 96  |

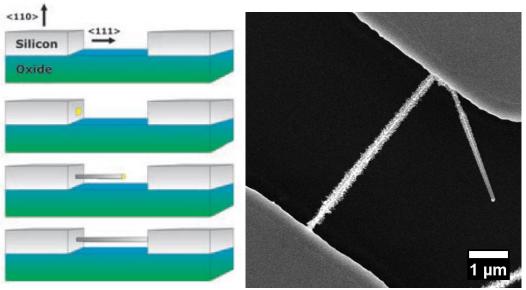

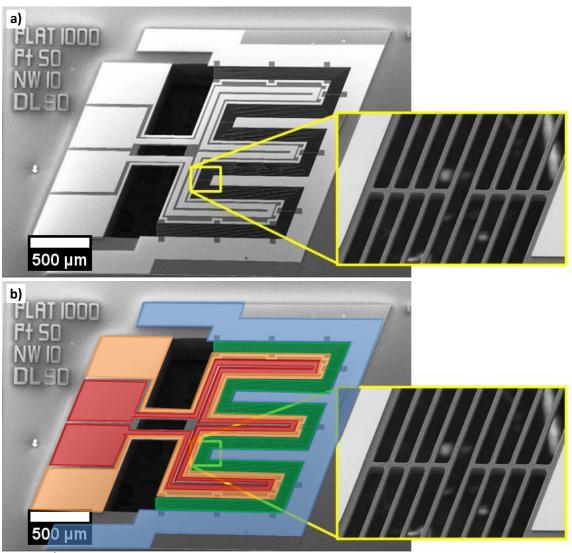

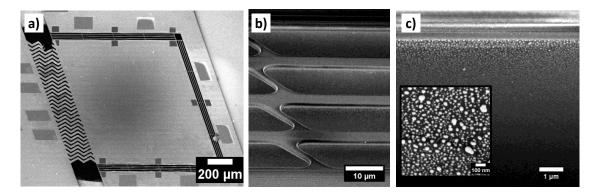

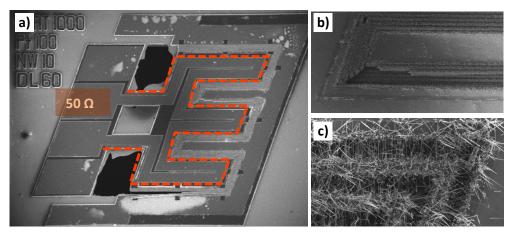

|    | 3.4. | NW           | integ      | gration in micro-devices                        | 99  |

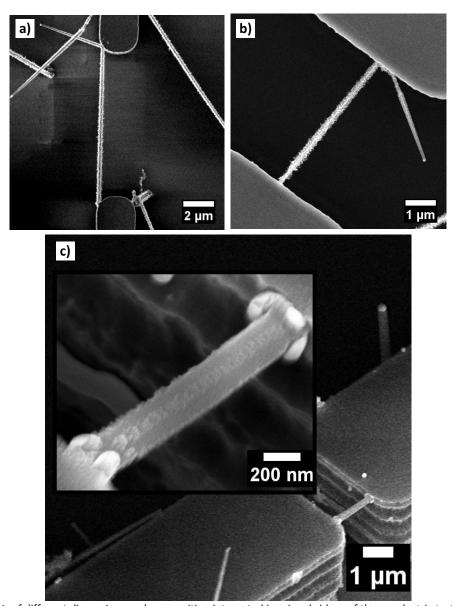

|    | 3.   | .4.1.        | Sing       | le NW integration in micro-bridges              | 99  |

|    | 3.   | .4.2.        | NW         | array integration in micro-trenches             | 101 |

|    |      | 3.4.2.1      | l.         | Galvanic displacement in micro-trenches         | 101 |

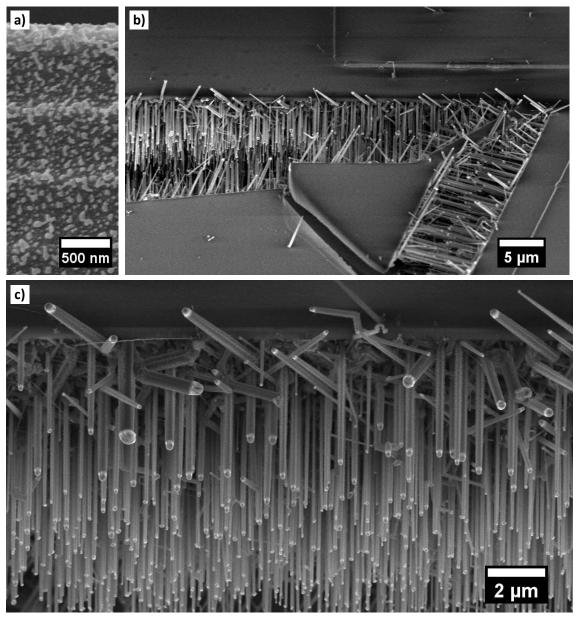

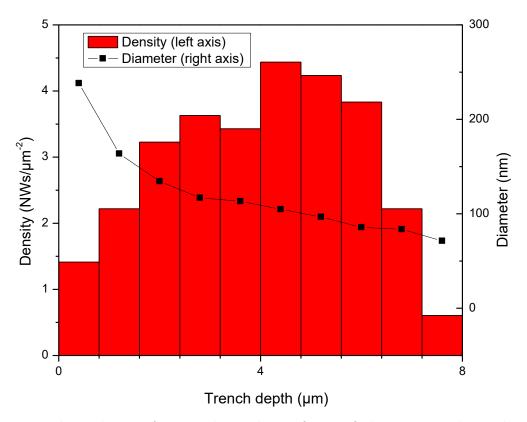

|    |      | 3.4.2.2      | 2.         | CVD-VLS NW integration in micro-trenches        | 106 |

|    | 3.5. | Con          | clusio     | on                                              | 109 |

| 4. | Si   | i NW TE      | char       | acterization                                    | 113 |

|    | 4.1. | Intro        | oduc       | tion                                            | 113 |

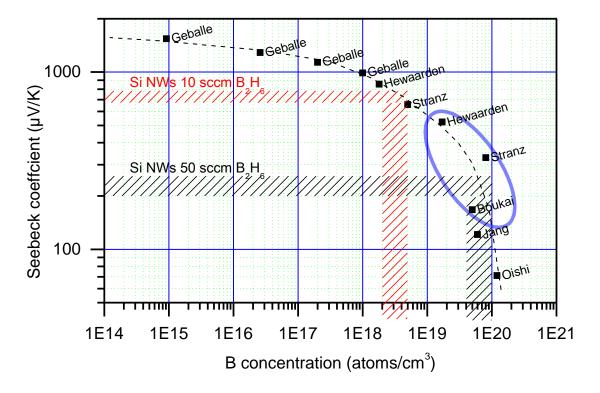

|    | 4.2  | <b>See</b> l | heck       | and doning control                              | 114 |

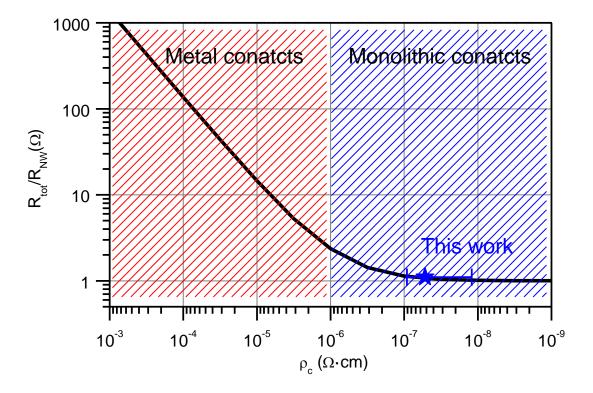

|    | 4.3. Electrical conductivity, power factor and contact resistance |          |                                                      |     |

|----|-------------------------------------------------------------------|----------|------------------------------------------------------|-----|

|    | 4.4.                                                              | The      | rmal conductivity                                    | 121 |

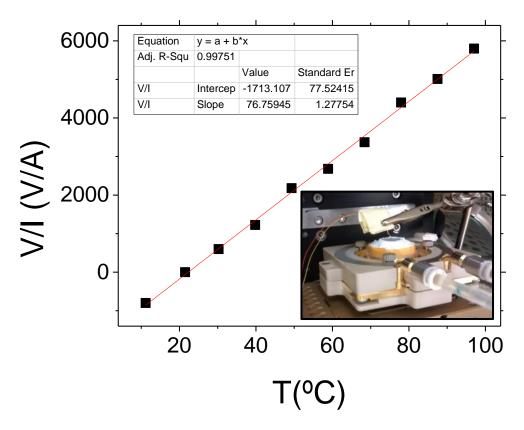

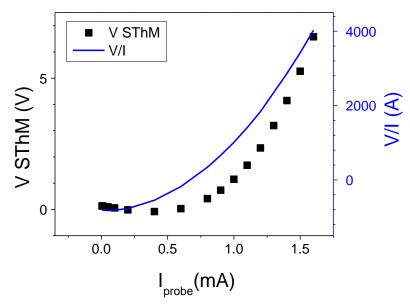

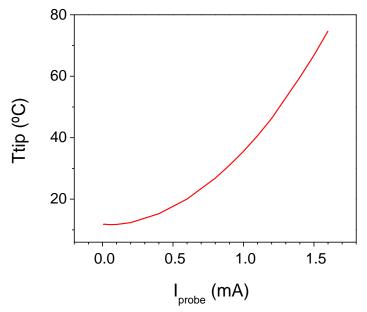

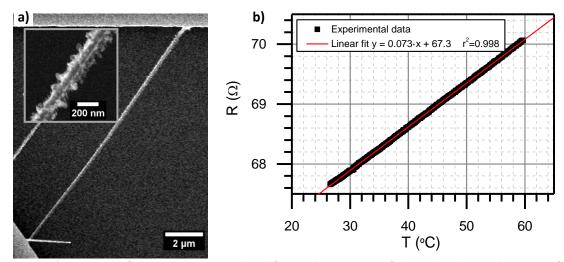

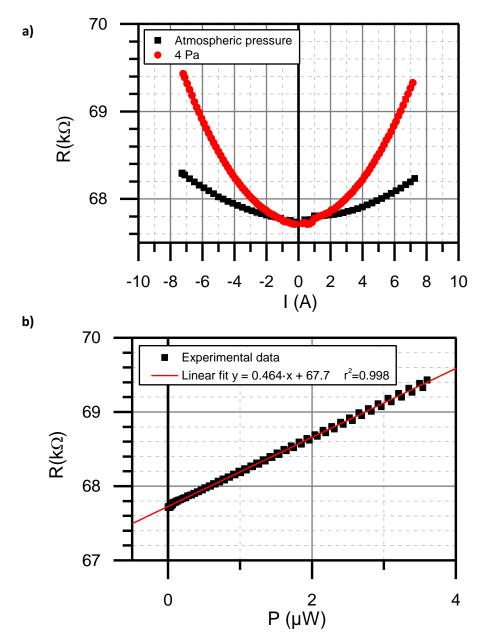

|    | 4.                                                                | 4.1.     | DC self-heating method                               | 121 |

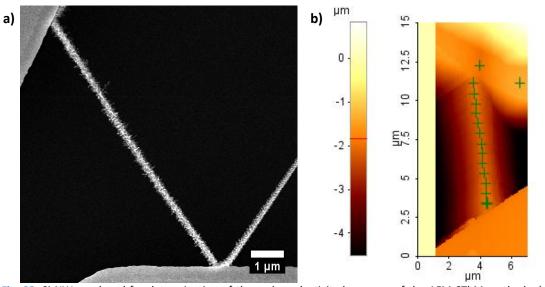

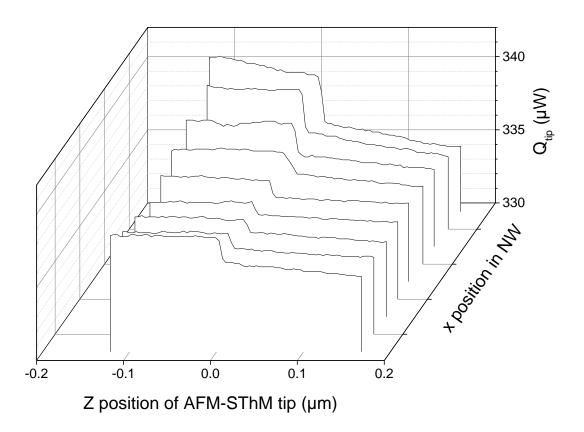

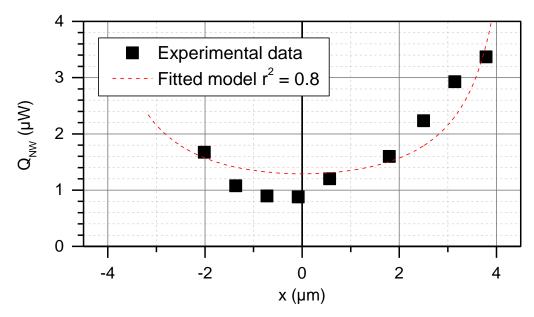

|    | 4.                                                                | 4.2.     | AFM-SThM method                                      | 125 |

|    |                                                                   | 4.4.2.1  | L. Method description                                | 125 |

|    |                                                                   | 4.4.2.2  | 2. Thermal conductivity measurement                  | 129 |

|    | 4.5.                                                              | Figu     | re of merit and conclusion                           | 132 |

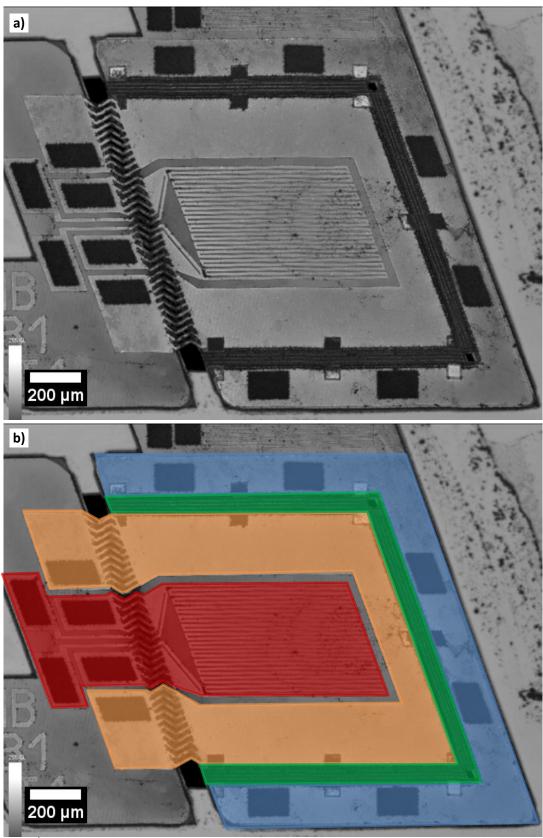

| 5. | Si                                                                | /Si-Ge   | NW based μTEG                                        | 134 |

|    | 5.1.                                                              | Intr     | oduction                                             | 134 |

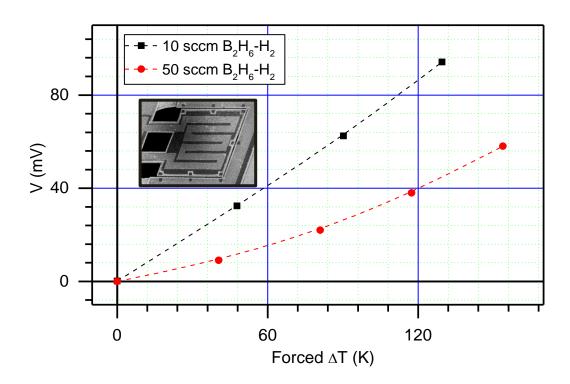

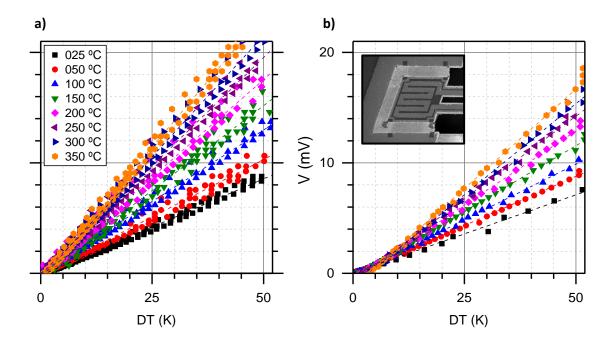

|    | 5.2.                                                              | See      | beck measurements from 25 to 350 ºC                  | 135 |

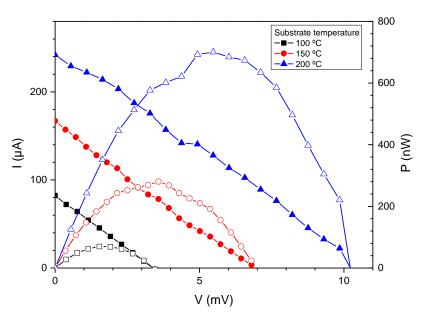

|    | 5.3.                                                              | Firs     | t generation structures                              | 138 |

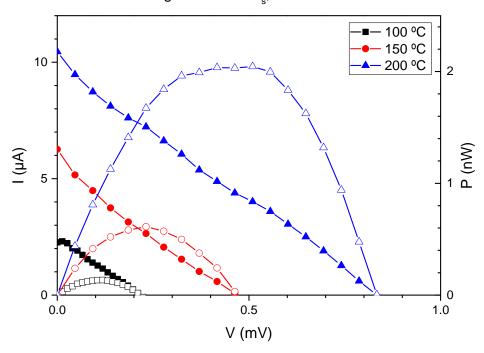

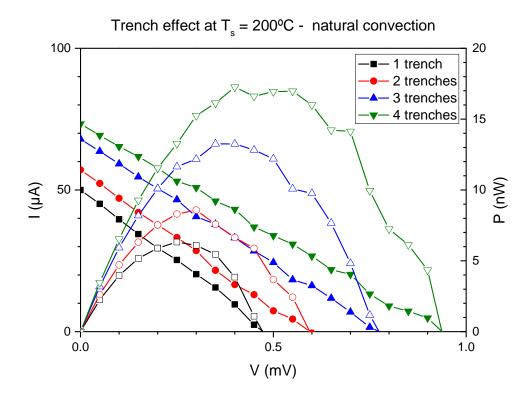

|    | 5.                                                                | 3.1.     | Si NW μTEG harvesting I-V and P curves               | 138 |

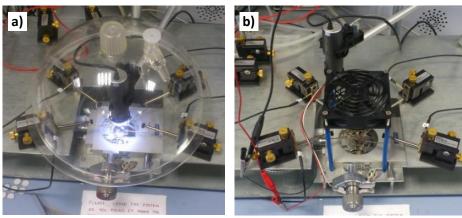

|    | 5.                                                                | 3.2.     | Si NW μTEG harvesting at forced convection           | 142 |

|    | 5.                                                                | 3.3.     | Micro-heat sink incorporation                        | 146 |

|    | 5.4.                                                              | Sec      | ond generation structures                            | 149 |

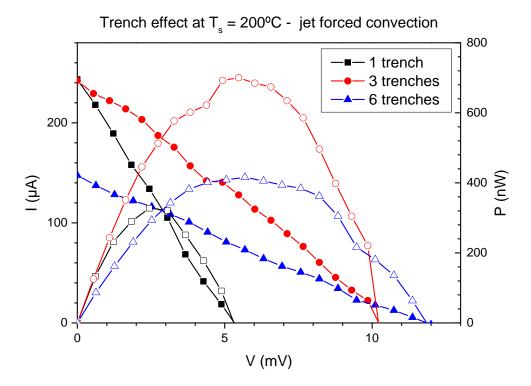

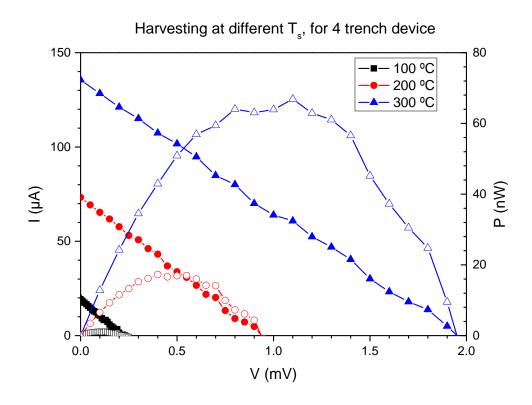

|    | 5.                                                                | 4.1.     | Si NW μTEG harvesting with second generation devices | 149 |

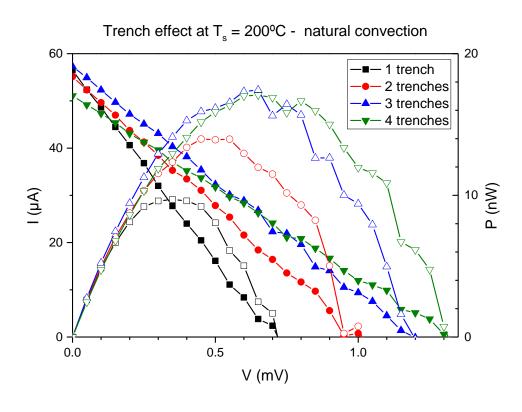

|    | 5.                                                                | 4.2.     | Si-Ge NW μTEG harvesting                             | 153 |

|    | 5.5.                                                              | Disc     | cussion and conclusion                               | 156 |

| 6. | p9                                                                | Si/Si-Ge | NT TE fabrics                                        | 161 |

|    | 6.1.                                                              | Intr     | oduction                                             | 161 |

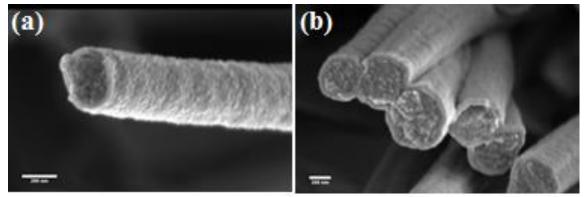

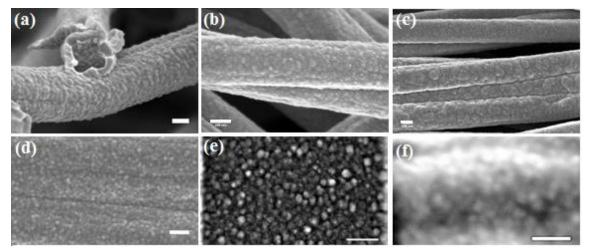

|    | 6.2.                                                              | Con      | cept and fabrication procedure                       | 161 |

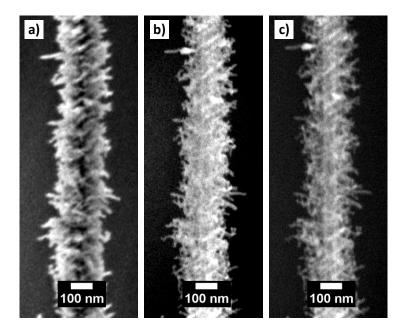

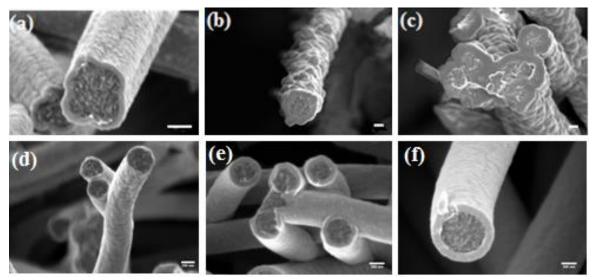

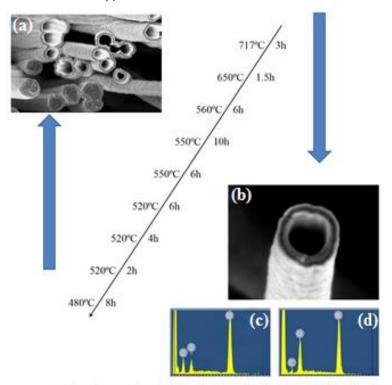

|    | 6.                                                                | 2.1.     | Influence of CVD deposition conditions               | 163 |

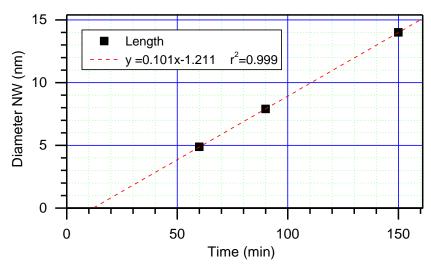

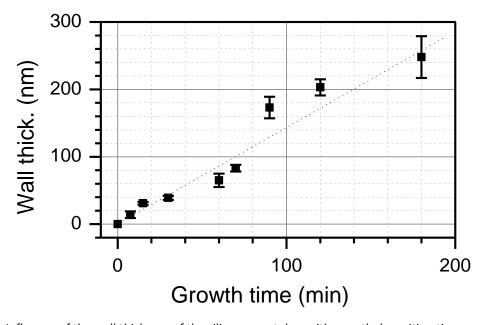

|    | 6.                                                                | 2.2.     | Growth rate at selected conditions                   | 166 |

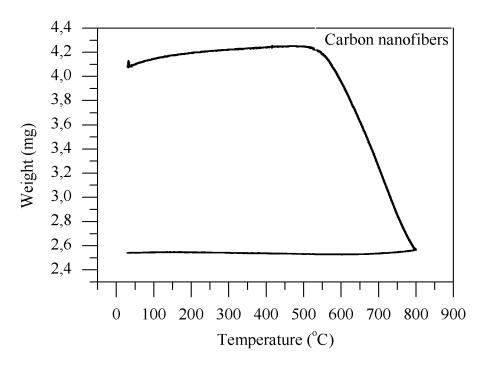

|    | 6.                                                                | 2.3.     | Release of sacrificial carbon core                   | 167 |

|    | 6.3.                                                              | The      | rmoelectric characterization of the system           | 169 |

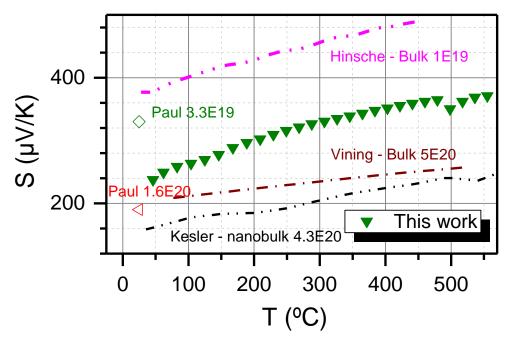

|    | 6.                                                                | 3.1.     | Seebeck coefficient                                  | 169 |

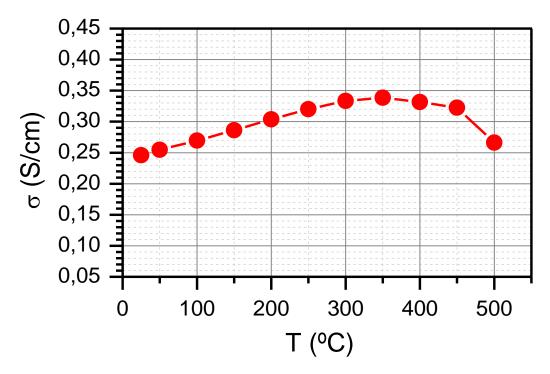

|    | 6.                                                                | 3.2.     | Electrical conductivity                              | 170 |

|    | 6.                                                                | 3.3.     | Thermal diffusivity and thermal conductivity         | 171 |

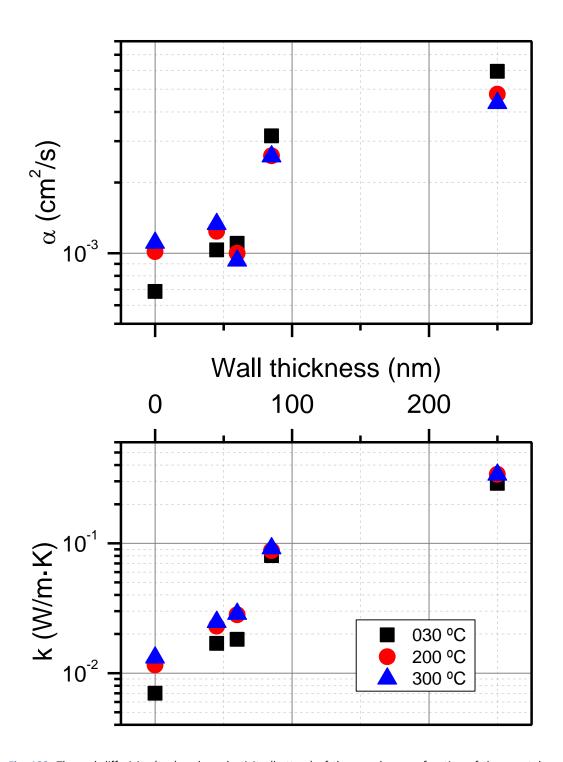

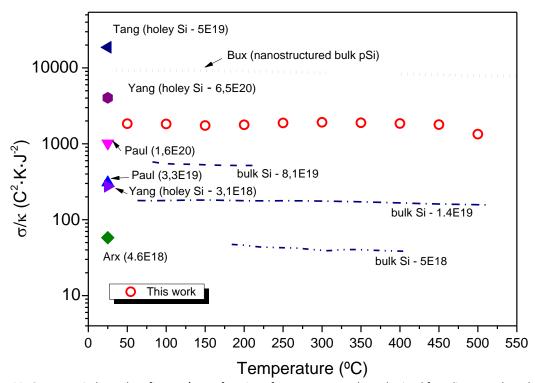

|    | 6.                                                                | 3.4.     | Electrical versus thermal conductivity (σ/κ factor)  | 173 |

|    | 6.                                                                | 3.5.     | Figure of merit (ZT)                                 | 175 |

|    | 6.4.                                                              | Pro      | of of concept: power generation                      | 175 |

|    | 6.5.                                                              | Con      | clusions                                             | 178 |

| 7. | Co                                                                | onclusio | ons                                                  | 181 |

|    |                                                                   | ncos     |                                                      | 192 |

### 1. Introduction

#### 1.1. Motivation

Thermoelectricity is the ability to convert temperature differences to electrical power or vice versa. Thermoelectric materials exhibit a strong thermoelectric effect, which is exploited in two kinds of devices:

- Thermoelectric generators (TEG), which generate usable power by putting them in contact with a hot and a cold surface.

- Thermoelectric coolers (TEC), which generate a cold surface (used to cool) and a hot surface by flowing current through them.

In terms of implementation thermoelectric devices present great advantages with respect to the conventional heat engines used for heat to power conversion (turbine systems) or power to cold conversion (compression based refrigeration). Their easy design without mobile pieces or fluids and their stability make them fully scalable and enable them for long term operation with absolute reliability and no maintenance requirements.

However, the conversion-efficiency/cost relation is behind that of their heat engine counterparts, which are used for efficiency demanding applications like power generation in thermal plants or cooling for air conditioning. Thermoelectric devices are thus used in applications where reliability, maintenance-free operation, size constraints and ease of use are most important, like TEGs for space missions and sensor node powering or TECs for portable cooling.

From the beginning of their application in the 1920s, research on thermoelectric materials has been focused in improving the efficiency/cost relation. Since 1990s the research on thermoelectric nanomaterials – namely, shrinking material dimensions to the order of 100 nm – has gained importance within the improvement strategies under research. Silicon presents a significant example, being able to increase its thermal-to-electrical conversion rate by a factor 100 when is in the shape of thin films or nanowires, with respect to its bulk counterpart [1], [2].

This work follows this line by two approaches:

- Rendering silicon an abundant and inexpensive material efficient enough by growing it in the shape of nanowires (NW) and nanotubes (NTs)

- Increasing Si-Ge an already efficient thermoelectric efficiency by growing it in the shape of NWs

However integration of nanomaterials into thermoelectric devices remains a hard task. For being able to exploit the thermoelectric effect large amounts of material need to be electrically connected to device ends available to generate temperature differences and collect current. Nanomaterial fabrication methods are such the resulting sizes are no just limited in the targeted dimension (diameter in nanowires, thickness in films), but in the three

dimensions. Namely, width and length of nanomaterials are constrained to the micrometer regime, making difficult the formation of a wide electronic path – able to circulate current – and a long thermal path – able to sustain thermal gradients.

In this work this limitation is overcome in two ways:

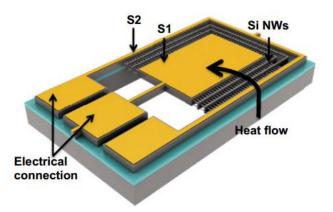

- Wide and dense arrays of  $\sim$  100 nm diameter NWs are integrated in microthermoelectric generators ( $\mu TEG$ ). NW arrays are also put in series to increase the length. NW-based micro-devices are able to generate a gradient and collect power at this scale in the order of the 1-10  $\mu W/cm^2$  range, suitable for energy harvesting applications.

- Polysilicon nanotubes of ~ 100 nm wall thickness grow packed in dense fabrics with overall dimensions in the cm range, easily scalable up to the meter. The fibers are electrically continuous along all fabric dimensions allowing direct utilization of this large-area nanomaterial for thermal harvesting, with power up to the 3.5 mW/cm2 for energy recovery.

It is worth to mention that the fabrication of the NW based  $\mu$ TEG device and the integration of NWs by Chemical Vapour Deposition (CVD) is done by mainstream microfabrication techniques used in clean rooms for IC production. Thus its expected overall cost is approximately that of a microchip. Regarding pSi nanotube fabrics the process is based in common techniques as well (electrospinning and CVD), both already well set in the commercial and technological framework.

Thus, main motivation of this work is being able to enhance and exploit thermoelectric effect of Si / Si-Ge for their application in thermal-to electrical energy conversion, referred as thermoelectric energy harvesting. This is intended for NWs based  $\mu$ TEGs and NT-based large area fabrics.

#### 1.2. Thermoelectric effect

The thermoelectric effect is the direct and thermodynamically reversible conversion of heat to electricity and vice-versa. This effect is explained in terms of the ability of electrons to carry heat and the effects of temperature in their random motion pretty much as free molecules in a gas.

The thermoelectric effect is encompassed by three differentiated effects that take name after the scientists who discovered them in the late XIX century.

The Seebeck effect, discovered by Johan Thomas Seebeck in 1821, consists in the generation of a voltage difference along the ends of a material which whose ends are kept at different temperatures. The open circuit voltage (OCV) developed is proportional to a constant value characteristic of the material and the temperature of the measurement, namely the Seebeck coefficient S.

$$\Delta V = -S \cdot \Delta T$$

Eq. 1

The origin of this effect is the difference between the random motion of charge carriers in the hot and cold end of the material. While in the hot end the charge carriers move at large speeds due to their high temperature, in the cold part they are much still. Despite the random movement of the carriers, the difference of speeds leads to net transport from the hot to the cold end as long as the thermal gradient is kept. The resulting charge imbalance is compensated by electric drift current, leading to an equilibrium scenario of null current where all the thermal gradient-derived flux is compensated by a electronic gradient-derived flux. The voltage difference measured along the material at this point is the Seebeck voltage described by Eq. 1.

The sign of the Seebeck coefficient depends on the sign of the majority charge carriers present in the material. Thus, for p-type semiconductors as boron doped silicon it is positive, since holes diffuse from hot end to cold end against the thermal gradient, and so voltage and gradient have opposed signs, as in Eq. 1 for positive S value. Conversely in n-type semiconductors or metals Seebeck is negative, as electrons are the ones diffusing, implying voltage and thermal gradients share sign, as in Eq. 1 for a negative S value.

The Peltier effect was discovered by Jean Charles Athanase Peltier in 1834. It consists in the release/absorption of heat at the junction of two dissimilar materials when current is forced through it. The amount of heat per unit time  $Q_{\Pi}$  is proportional to the current I and the difference of two constants – the Peltier coefficients  $\Pi$  –, each one characteristic of the material and dependent in temperature.

$$Q_{\pi} = (\Pi_A - \Pi_B) \cdot I$$

Eq. 2

Depending on the magnitude of the coefficients (which are always positive) and the direction of the current, heat is absorbed or released at the junction. This effect is explained as the different capacities of carrying heat of the carriers in dissimilar materials.  $\pi$  coefficients represent the thermal energy per unit charge of a charge carrier within a specific material. When current flows through a junction the thermal energy per unit charge is suddenly changed, resulting in carriers being forced to either release heat to the surrounding material – heating up the junction – or absorb it from the latter – thus cooling down the junction.

Thompson effect, discovered by Lord Kelvin (William Thomson) in 1851 is the release/absorption of heat within a material subjected to both a thermal gradient and a current flow. Heat per unit volume and time  $Q_{\kappa}/V$  is released at a rate proportional to the thermal gradient, the current flux J and a constant  $\kappa$ , namely the Thompson coefficient characteristic of the material.

$$\frac{Q_{\kappa}}{V} = \kappa \cdot J \cdot \Delta T$$

Eq. 3

This effect is explained as a continuous version of the Peltier effect. Since Peltier coefficient is temperature dependent, when current flows though a material subjected to thermal gradient the carriers change their heat capacity and are forced to release/absorb heat locally.

The coefficients involved in the three effects are related by means of the Thompson relations, found by Kelvin in 1854 and proven by Lars Onsager in 1931. These two relations are

demonstrated applying statistical mechanics to microscopically reversible systems, and state the relations among these coefficient and absolute temperature T:

$$\kappa = \frac{\mathrm{d}\Pi}{\mathrm{d}T} - S$$

Eq. 4

$$\Pi = T \cdot S$$

#### 1.3. Thermoelectric devices

#### 1.3.1. Applications of the thermoelectric effect

The thermoelectric effect can be exploited in two ways in order to develop devices with functional applications, namely thermoelectric generators (TEG) and thermoelectric coolers (TEC).

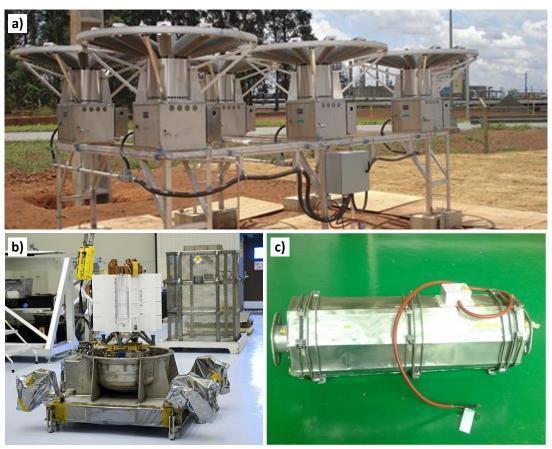

In thermoelectric generators a material exhibiting a strong Seebeck coefficient is electrically connected to a consuming load and subjected to a thermal gradient. The Seebeck voltage generated this way is used to generate a current that powers the load, converting part of the thermal energy flowing trough the material to electrical energy. Fig. 2 shows commercial thermoelectric generators used in pipeline maintenance applications, space missions and automotive sector.

Fig. 2. Commercial thermoelectric generators (TEG). a) TEGs coupled to burners in gas pipelines, from *GenTherm*. Their function is to power remote devices for maintenance. b) Radioisotope Thermoelectric Generator (RTG) used for space missions, in *Mars Science Laboratory*. c) TEG module for coupling to car exhaust pipes, converting energy

from the hot combustion gases to charge the battery, from *Thermonamic*.

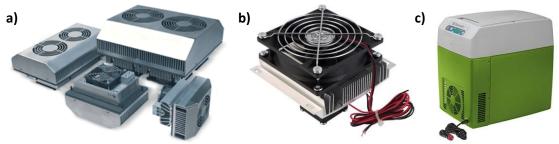

On the other hand in thermoelectric coolers force current through junctions comprising materials with highly dissimilar Peltier coefficients (S·T), namely a thermoelectric material (high S) and a metal (low S). This allows exploitation of the Peltier effect by cooling and end of the material, transferring the heat to the other end. This way, thermoelectric coolers are able to pump heat out of a targeted surface and thus using thermoelectric effect for cooling applications. Fig. 3 shows commercial thermoelectric coolers.

Fig. 3. Commercial thermoelectric coolers (TEC). a) thermoelectric based air conditioners for application in harsh environments, from *Rubsamen&Herr*. b) TEC for microprocessor cooling, from *XuMarket*. Portable TEC for cooling of food/drinks, from *Dometic*.

#### 1.3.2. Thermoelectric device design

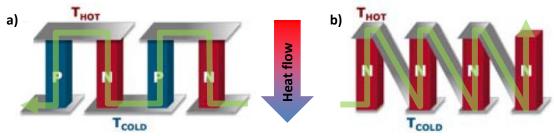

The power supplied by thermoelectric generators is proportional to the area of thermoelectric material subjected to the thermal gradient. While Seebeck voltage generated by a piece of thermoelectric material (Eq. 1) is not dependent on its shape, the current that flows through it by means of the Ohms lay is so, as it is proportional to the cross section. Thus higher will increase the power proportionally by increasing the current in the same factor. However optimal transmission of power to the load is generally attained at higher voltages that that supplied by a single chunk of thermoelectric material. For this reason thermoelectric generators are often designed as depicted in Fig. 4, putting many pieces of thermoelectric elements in electrically in series and thermally in parallel.

Fig. 4. two-leg (a) and mono leg (b) architectures for increasing output voltage of thermoelectric devices, adapted from [3]. P and N indicate p and n-type semiconductors respectively, namely with different Seebeck signs. arrows indicate the sense of the positive current flow.

In two-leg thermoelectric devices materials with different Seebeck coefficient sign (n and p-type semiconductors) are joined electrically in a meandering manner with alternate metal contacts joining each two consecutive pieces of material, referred as legs (Fig. 4a). This way Seebeck voltages are generated always in the direction of current (Eq. 1), adding up in series to attain a higher voltage. The electric path however has the cross section of a single leg, meaning

that the current is not increased by increasing contact area with cold/hot ends — namely increasing leg number. Thus, this configuration, commonly used in TEG design leads to increase of power by multiplying the voltage, rather than the current with increasing area. The mono-leg architecture shown in Fig. 4b attains the same effect with the use of a single type of thermoelectric material, always with the same Seebeck sign, and a different interconnection pattern.

High-voltage/low-current powers are preferred to low-voltage/high-current powers due to the generally high voltage demanding end loads that are connected to the devices and the minimum input required by the most efficient DC-DC boot converters [4]. For this reason thermoelectric devices are mostly design in this multi-leg manner, and conventional thermoelectric modules follow the design shown in Fig. 4. This architecture is also extended to TECs in which the same argumentation can be applied in terms of power that needs to be supplied: series connection of elements leads lo higher voltage and lower currents demands for achieving the same cooling rate.

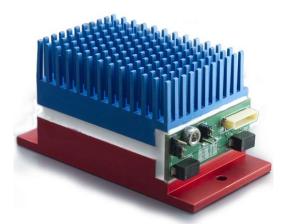

In thermoelectric generators in which the hot part is an underlaying surface and cold part is cooled by – air as in this work – there is usually a heat sink incorporated as shown in Fig. 5. The purpose of the heat sink is effectively lowering temperature by enhancing air-cold end surface and thus generating a higher Seebeck which leads in turn to a higher power.

Fig. 5. TEG for harvesting on top of hot surfaces, from [5]. The design features a heat sink on top – for cooling with the air – and a pierced plate on bottom for screwing onto hot surfaces.

#### 1.3.3. Device efficiency

When a thermoelectric material is connected for thermoelectric generation properties then the Seebeck coefficient come into play influencing the power supplied by the device. These are electrical conductivity  $\sigma$  and thermal conductivity k, which define the rates at which current I and heat flow Q are transferred within the material according to Ohm and Fourier's laws:

$$I = \sigma \cdot \frac{A}{L} \Delta V$$

Eq. 6

$$Q = k \cdot A \frac{\Delta T}{I}$$

Eq. 7

where L and A are the length and cross section of the material respectively.

The heat absorbed at the hot end of the material is given by:

$$Q_H = STI + kA\frac{\Delta T}{L} - \frac{1}{2}\frac{L}{\sigma A}I^2$$

Eq. 8

The first term is the Peltier heat absorbed at the junction with the metallic current collector, which has S  $\sim$  0 and thus  $\pi$   $\sim$  0 (Eq. 2, Eq. 5). The second term is the heat that goes to the cold end away by thermal conduction through the material (Eq. 7) . The third term corresponds to half the joule heating (RI², Eq. 6) released in the material due to the current flow – the other half goes to the cold end.

The power supplied (/consumed by) an electric load of resistance R<sub>load</sub> which is connected in series with the TEG is given by:

$$P = R_{load}I^2$$

Eq. 9

Ohm's law applied to a series circuit comprising the TEG voltage source (V=S· $\Delta$ T, Eq. 1), the TEG resistance  $\frac{L}{\sigma A}$  (Eq. 6) and the road resistance R<sub>load</sub>, leads to:

$$I = \frac{S\Delta T}{R_{load} + \frac{L}{\sigma A}}$$

Eq. 10

Combining Eq. 8, Eq. 9 and Eq. 10 leads to the relation between power supplied to the load (P) with material properties  $(S, \sigma, k)$ , and external conditions  $(\Delta T, R_{load})$ . Maximization of the power is attained when resistance of the load is matched with that of the thermoelectric material. Introducing  $R_{load} = \frac{L}{\sigma A}$  leads to the following expression which defines device efficiency in converting thermal to electrical power  $\eta$  [6]:

$$\eta = \frac{T_h - T_c}{T_h} \frac{\sqrt{1 + ZT} - 1}{\sqrt{1 + ZT} + \frac{T_c}{T_h}}$$

Eq. 11

where the efficiency  $\eta$  is defined as power delivered to the load (P, Eq. 9) divided by heat absorbed by the device (Q<sub>H</sub>, Eq. 8). T<sub>h</sub> and T<sub>c</sub> are the temperature of hot and cold ends respectively and ZT an adimensional number referred as the thermoelectric figure of merit including the properties of interest, defined as:

$$ZT = \frac{S^2 \sigma T}{k} = \frac{S^2 \sigma}{k} \cdot \frac{T_h + T_c}{2}$$

Eq. 12

When a two-leg material is considered, S,  $\sigma$  and k are averaged from the values of both legs.

An analogous development for thermoelectric coolers yields to the coefficient of performance (COP) as a function of ZT and temperatures:

$$COP = \frac{T_c}{T_h - T_c} \frac{\sqrt{1 + ZT} - \frac{T_c}{T_h}}{\sqrt{1 + ZT} + 1}$$

Eq. 13

where the COP is defined as power removed at the cold junction/power supplied to the TEC.

As ZT increases the efficiency in Eq. 11 increases, tending to the Carnot efficiency for a heat engine  $\frac{T_h - T_c}{T_h}$ . As ZT increases the COP in Eq. 11 increases, tending to the Carnot COP for a refrigerator  $\frac{T_c}{T_h - T_c}$ .

In micro-thermoelectric generators as the one contemplated in this work the Peltier effect is disregarded due to the minimum influence of the small thermoelectric material into the relatively larger by comparison  $\mu TEG$ . Also a series thermal resistance is considered between the cold part at Tc and the actual cold sink at invariable temperature Ts – the air in this work. This done because it has been experimentally proven that temperature in the cold end of the material is not that of air, as will be discussed in Chapter 5. In this case the simpler model used by Leonov is considered [7], which leads to the power attained by a  $\mu TEG$  harvesting on top of a source at Th, cooled by air at Ts:

$$P = Z \cdot (T_h - T_s)^2 \cdot \frac{f(1-f)}{4R_s}$$

Eq. 14

Where A is thermoelectric material cross section,  $Z = S^2 \sigma T/k$  is defined as in ZT,  $R_s$  is the thermal resistance of the cold of the device to the heat sink at temperature Ts, and f an adimensional thermal matching factor, defined as:

$$f = \frac{T_h - T_c}{T_h - T_s} = \frac{R_{TE}}{R_{TE} + R_s}$$

Eq. 15

That is, f is the fraction of thermal gradient that falls in the thermoelectric with respect to the external thermal gradient  $T_h-T_s$  applied, which is given by the ratio of thermal resistance of the thermoelectric  $R_{TE}$  with that of the thermoelectric and sink in series  $R_{TE}+R_s$ . In this case performance of the device depends on the material in two senses: in Z value which is directly proportional to the power and in achieving an effective thermal matching, which depends also in the thermal resistance of the sink  $R_s$  given by the device. This matching effect is analogous to electrical impedance matching, and so  $f \cdot (1-f)$  is maximized when  $R_{TE} = R_s$ . In bulk thermoelectric modules the effect is also present and taken into account, using a specific fill factor and length of the device legs to match the thermal resistance of material with that of the attached sink.

In al cases (Eq. 12, Eq. 13, Eq. 14) device performance increases with Z. Thus, thermoelectric figure of merit ZT is used to compare thermoelectric performance of materials. Typical commercial thermoelectric materials have ZT  $^{\sim}$  1, leading conversion efficiencies of  $\eta$  = 5 - 15% (Eq. 12).

The equations presented herein where applied for materials ideally integrated in devices without parasitic thermal/electrical resistances. In real cases all contact resistances material-

device are added in series diminishing effective  $\sigma$  of the device, and all thermal parallel paths are contributing to rise k of the device. Thus, real efficiency of the  $\mu$ TEGs is a function of both material and device aspects.

#### 1.4. Thermoelectric materials

#### 1.4.1. Materials for high ZT – intercorrelation of TE properties

In order to have high ZT – i.e. thermoelectrically performant – materials one must achieve a high Seebeck coefficient S, a high electrical conductivity  $\sigma$  and a low thermal conductivity k, according to definition of ZT (Eq. 12). S,  $\sigma$  and k (referred as the thermoelectric properties of a material) are however strongly intercorrelated by nature. Eq. 12 can be extended in order to distinguish the influence of electron and phonon contributions to the thermoelectric properties:

$$ZT = \frac{S^2 \sigma T}{k} = \frac{\left(S_e + S_{ph}\right)^2 \sigma T}{k_e + k_l}$$

Eq. 16

The Seebeck coefficient can be regarded as the sum of the electronic contribution  $S_e$  and the phonon drag effect  $S_{ph}$ . The first contribution is arisen from the effect mentioned section 1.2 of different charge carrier diffusion rates at different temperatures. This is given by the Mott formula, applicable to metals and degenerated semiconductors [8]:

$$S_e = \frac{\pi^2}{3} \left( \frac{k_B^2 T}{e} \right) \left( \frac{d ln(\sigma)}{dE} \right)_{E=E_F}$$

Eq. 17

Where kB is the Boltzmann constant and E the energy level, and  $E_F$  the fermi level. Though not straight evident from Eq. 22,  $S_e$  has a decreasing tendency with increasing  $\sigma$ .

The phonon drag contribution  $S_{ph}$  arises from the collisions of phonons – lattice vibrations carrying heat, treated as quasiparticles – with electrons. When a material is subjected to thermal gradient the phonons transport heat from the hot to the cold part interacting in their way with charge carriers. This interaction may be regarded as drag of the carriers further towards the cold end, contributing positively to Seebeck effect. This contribution looses weight with respect to electrical one as temperature is increased.

Regarding thermal conductivity, the lattice thermal conductivity  $k_l$  is the contribution to heat flow arisen by the aforementioned phonon transport. Increasing temperature and impurities in the material lead to reduction of this contribution, as phonons find more scattering mechanisms, namely other phonons and impurities.

The contribution to electronic conductivity  $k_e$  is that of the charge carriers, which carry also heat as introduced in section 1.2. This is related with electronic conductivity by the Wiedemann-Franz law [8]:

$$k_e = \frac{\pi^2}{3} \left(\frac{k_B}{e}\right)^2 \sigma T$$

Eq. 18

Eq. 22 and Eq. 23 intercorrelate the electronic related parameters of ZT, namely  $\sigma$ ,  $S_e$  and  $k_e$ . The relation is such that when  $\sigma$  conductivity is raised (positive for ZT), so is  $k_e$  (negative for ZT) whereas ,  $S_e$  is lowered (negative for ZT), and conversely if  $\sigma$  is lowered. Thus the electronic magnitudes are linked so that an optimum ZT is found at a specific  $\sigma$  for each material.

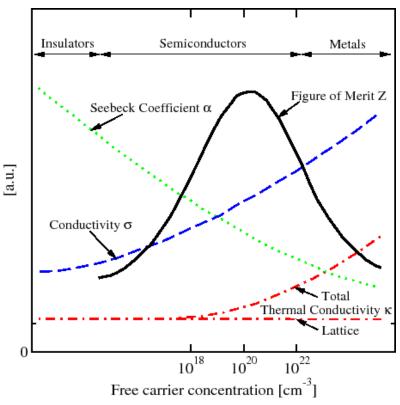

As insulators are unable to electrically conduct and metals have a very low Seebeck coefficient, thermoelectrically efficient materials are heavily doped semiconductors.  $\sigma$  is controlled in semiconductors by impurity doping. The aforementioned effect of electronic TE property interlinking is illustrated at Fig. 6 showing an optimum impurity concentration where ZT is maximized.

Fig. 6. variation of thermoelectric properties (S,  $\sigma$  and k) and ZT with carrier concentration (illustrative plot), taken from [9]. Lattice thermal conductivity contribution is indicated.

Thermoelectric properties change considerably with temperature. The dependencies on  $S_e$  and  $k_e$  are already recognizable in Eq. 22 and Eq. 23. Electrical conductivity changes also with temperature, decreasing for highly doped semiconductors due to the increased phonon-electron scattering, and so does lattice contribution to thermal conductivity. All in all results in an optimum temperature od application for each thermoelectric material family.

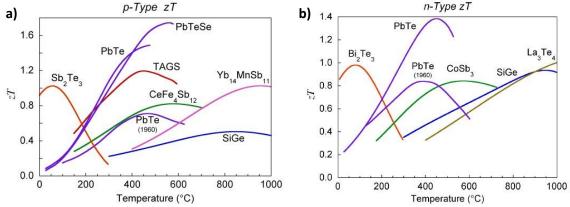

Fig. 7 shows plots of ZT of diverse archetypical thermoelectrics with respect to temperature. The main families for room temperature application are chalcogenide based, as the popular thermoelectric modules used for thermoelectric cooling applications. At the other end there is the Si-Ge and the Half-Heuslers, which exhibit a reduced thermal conductivity due to mass-difference phonon scattering.

Fig. 7. common thermoelectric materials with different optimum temperatures for operation, indicated by the ZT peak. a) p-type doped materials. b) n-type doped materials. Taken from [10].

#### 1.4.2. Si/Si-Ge nanostructured materials

Due to the strong intercorrelation between  $\sigma$  and Se – which is the major contribution to S as we go above room temperature - , the power factor PF = S· $\sigma$  is hard to improve by other means than achieving an optimum doping of the semiconductor, as in Fig. 6. However in k a significant contribution comes form the lattice component  $k_l$ . Thus there has been a lot of effort directed towards reduction of the lattice thermal conductivity, which can be done without influencing electronic parameters. This is attained by introduction of additional scattering mechanisms for the phonon transport and thus is referred as phonon engineering. In this work this approach was applied to in Si/Si-Ge nanostructures in order to improve their thermoelectric performances, in two differentiated manners, namely Si-Ge alloying and nanostructuration.

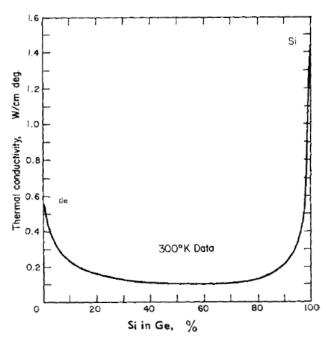

**Si-Ge alloying.** By alloying Si with Ge a significant reduction of thermal conductivity with respect to pure Si or pure Ge can be attained. This is due to enhanced mass-difference phonon scattering [6]. This scattering mechanism is based on the different masses of the elements composing a crystal cell. As the atoms of Si and Ge are randomly distributed, this difficults the propagation of short wavelength phonons, hindering the heat transports. The more disordered the better, thus a minimum of thermal conductivity is achieved when the concentration is 50%- Si-50% Ge. However the range in which this effect takes place is quite large as appreciated in Fig. 8, and germanium is an expensive material. Is for this reason that Si-Ge alloys used in thermoelectric applications have often compositions of 20-30% Ge, as increasing further more the Ge content does not lead to significant improvement and increases price.

Fig. 8. Variation of thermal conductivity of Si-Ge alloys with Ge concentration, taken from [11].

**Nanostructuration.** As predicted by Hicks and Dresselhaus [1], [2], the thermoelectric materials increase their figure of merit when their dimensions are diminished to the nanoscale, as in the case of NWs. Quantum confinement effects increase the electrical conductivity and the Seebeck coefficient, while reduced material dimensions limit the mean free path of phonons. This last effect, know as phonon boundary scattering, allows a reduction of thermal conductivity without affecting the rest of thermoelectric properties. This is so because phonons have mean free paths in the order of 100-300 nm in Si/Si-Ge NWs, while in electrons this length is in the order of 2 nm. Thus, when drifting from the hot to the cold end, phonons are more prone to reach surface and be scattered randomly, affecting their mean propagation velocity.

This effect can be applied to NWs, but as well to thin films and nanograins, as long their characteristic dimensions – NW diameter, film thickness and grain size respectively – are in the order of the phonon mean free path.

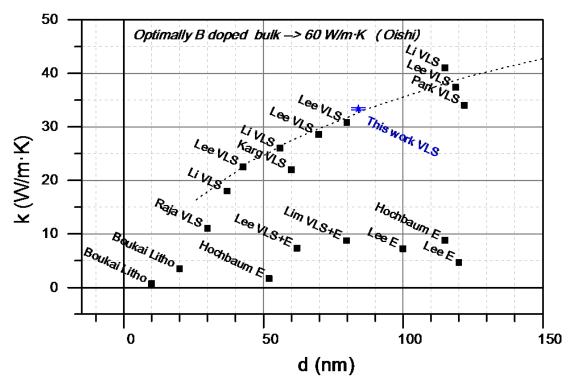

Some examples of nanostructuration of Si materials comprise the work of Boukai et al, which reported ZT as high as 0.35 at room temperature for 20 nm Si NWs, with a thermal conductivity of 3.5 W/mK. This is significant since the bulk values of ZT and thermal conductivity at room temperature are 0.01 and 150 respectively [12]. Hochbaum et al. reported an even higher improvement, with a k of 1.7 W/mK and a ZT of 0.65 at room temperature, attributing the effects to an enhanced phonon scattering by rough surface of the NWs, that were obtained by rough etching methods [13]. Regarding other Si Valalaki et. all reached a ZT 0.033 in bulk pSi thin films of 100 nm thickness and grain sizes of 50 nm [14]. Kessler et al. report ZT 0.05 at 100  $^{\circ}$ C for pSi with grain sizes of 43 nm [15]. In these fine grained samples the relation of  $\sigma$ /k was not so high but they presented an additional nanostructured effect that raised ZT, namely energy filtering. This effect is due to energy-dependent electron scattering mechanisms at grain boundaries, which increase the electronic contribution of the Seebeck coefficient.

Regarding Si-Ge, unlike in silicon the bulk already has high values apt for application, due to the aforementioned alloying-derived thermal conductivity reduction. For instance they are used in Radioisotope Thermoelectric Generators (RTGs) in space missions, with ZT peaks of 0.5 at 850 °C for p-type and 0.9 at 900 °C for n-type. Joshi et al. synthetized p-type pSiGe in fine grains of 15-20 nm, reporting a ZT of 1 at 750 °C, and a reduction of k from 4 W/mK (p-type RTGS) to 2.5 W/m·K [16]. Wang et all reached ZT of 1.3 at 900 °C with n-type pSi-Ge of 22 nm grain size [17]. Regarding NWs, Martinez et al. characterized p-type Si-Ge NWs at room temperature, which yielded ZT of 0.16, in comparison to corresponding bulk 0.09 [18]. Lee et al. reported a ZT of 0.2 for n-type Si-Ge NWs at room temperature. Kim et al reported an important effect of roughness in Si NWs as well, as thermal conductivity could be lowered from 7.5 to 2.5 W/mK for NWs essentially equal except in their surface roughness [19].

With Si and Ge additional structures can be attained providing further mechanisms for ZT enhancement. Li et al. grew superlattice Si/Si-Ge NWs, with defined interphases by a CVD-PLD, but concluded that alloy scattering was the dominant effect in these wires [20]. Wingert et al reported very low k of 1 W/mK in Ge/Si core/shell NWs with enhanced electrical conductivity suggesting a good architecture thermoelectric application [21].

### 2. Experimental

#### 2.1. Nanostructure growth and integration

#### 2.1.1. Chemical Vapour Deposition – technique and reactor

The Si/Si-Ge nanostructures grown in this work were obtained by means of the chemical Vapour Deposition method (CVD). This is a well known technique in the microfabrication which essentially consists in flowing precursor gases through a reactor containing a solid sample, while controlling conditions as temperature, pressure and reactant flows of reactants/carriers. The precursors decompose in contact with the sample, that serves as a nucleation center, leading to a deposition of the material of interest [22]. Further details on nanostructure growth processes are given in subsequent sections.

The CVD reactor used in this work was a commercial First Nano EasyTube 3000, located at IREC facilities in Nanoionics Lab (Fig. 9). The system comprised a quartz tube with two pressure sensors (for 0-10 Torr and 10-850 Torr respectively) and three thermocouples (for different locations within sample holder). A set of three resistances surrounding the quartz tube and a rotatory pump allowed deposition controlling temperature up to 750 °C and pressure from 0.5 to 50 Torr. The reactor also controlled the flows all the injected gases with a set of mass-flow controllers.

Fig. 9. CVD reactor EasyTube 3000 from FirstNano at IREC facilities, employed for nanostructure growth in this work Table 1 summarizes the properties of the gases fed to the in the CVD reactor during the nanostructure growth processes carried in this work.

Silane (SiH<sub>4</sub>) and germane (GeH<sub>4</sub>) were used as precursors for deposition of Si, Ge and Si-Ge in two kinds of nanostructures, namely Si/Si-Ge nanowire arrays and Si nanotube fabrics.

Diborane ( $B_2H_6$ ) was used as a precursor for in-situ doping of the nanostructures during growth. Hydrogen was used as carrier of the aforementioned gases and as solvent for controlling partial pressure of precursors, which could be rather high for suitable growth if undiluted gases were used. In NW growth hydrochloric acid (HCl) was used as well in order to control important aspects of the resulting morphology, as will be detailed in following sections. While  $GeH_4$ ,  $SiH_4$  and  $B_2H_6$  were  $H_2$ -diluted and in gas phase in their source bottles, HCl was pure and liquefied – though evaporated prior to its injection to CVD system. Thus, in all cases the precursors/reactants were fed as gases to the CVD system.

Table 1. Properties of gases involved in CVD process

| Gas                                       | Function                              | Composition                                        | Flow range allowed by CVD system (sccm) |

|-------------------------------------------|---------------------------------------|----------------------------------------------------|-----------------------------------------|

| Hydrogen (H <sub>2</sub> )                | Carrier, solvent                      | 99.999% pure H₂                                    | 100-1000                                |

| Silane (SiH <sub>4</sub> )                | Silicon precursor                     | Diluted, 10% SiH <sub>4</sub> , 90% H <sub>2</sub> | 5-200                                   |

| Germane (GeH₄)                            | Germanium precursor                   | Diluted, 10% GeH <sub>4</sub> , 90% H <sub>2</sub> | 5-200                                   |

| Diborane (B <sub>2</sub> H <sub>6</sub> ) | Boron precursor, for<br>p-type doping | Diluted, 7500 ppm in H <sub>2</sub> .              | 2-50                                    |

| Hydrogen chloride<br>(HCl)                | Auxiliary for NW morphology control   | 99.999% pure HCl, liquefied                        | 2-100                                   |

| Argon                                     | Venting                               | 99.999% pure Ar                                    | 100-5000                                |

In a typical CVD process for growing Si/Si-Ge nanostructures the following steps would be followed:

Table 2. Steps of a CVD process for nanostructure growth

| Phase       | Step                                                                          | Details                                                                                 |  |

|-------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|

|             | Sample loading                                                                | At room conditions                                                                      |  |

|             | Air evacuation till 150 mTorr                                                 |                                                                                         |  |

| Pre growth  | Chamber fill with H2, and setting of pressure to $P_{\text{growth}}$          | P <sub>growth</sub> set to 0.5-20 Torr                                                  |  |

|             | Heating ramp, from room temperature to T <sub>growth</sub>                    | T <sub>growth</sub> set to 500-700. Ramps of 1h.                                        |  |

| Growth      | Stabilization of conditions prior to injection                                | Temperature and flows are checked to be stable at desired conditions for following step |  |

|             | Injection of precursors/HCl during controlled growth time $t_{\text{growth}}$ | t <sub>growth</sub> from 5 to 180 min                                                   |  |

|             | Cooling in H <sub>2</sub>                                                     | Pressure still at P <sub>growth</sub>                                                   |  |

| Post growth | Venting chamber with argon                                                    | Pressure restored to ambient                                                            |  |

|             | Sample unloading                                                              | At room conditions                                                                      |  |

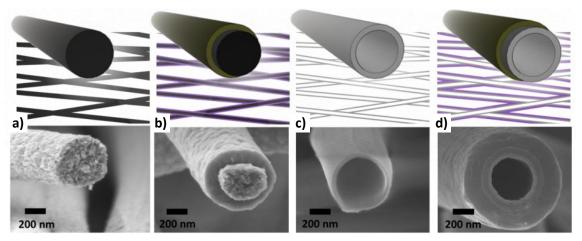

#### 2.1.2. VLS growth for Si/Si-Ge nanowires

#### 2.1.2.1. Growth mechanism and chosen precursors

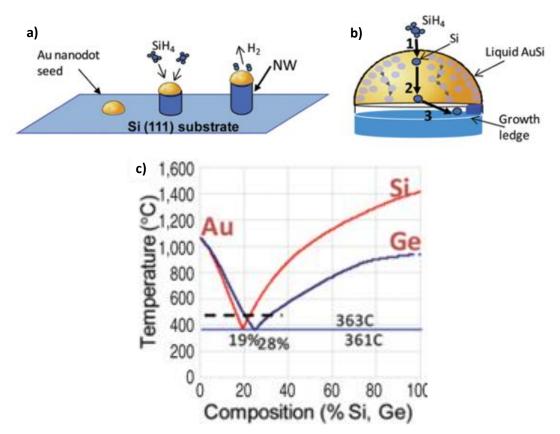

Si/Si-Ge NWs were grown using a CVD-based growth method known as the Vapour-Liquid-Solid growth. This growth mechanism was discovered by Wagner and Ellis in 1964 and is currently well know and used for obtaining NWs of various materials, chiefly doped semiconductor NWs [23]. The method mechanism is illustrated at Fig. 10 for the growth of Si NWs from silane (SiH<sub>4</sub>) though it is compatible with other materials/precursors.

Fig. 10. a, b) schematics showing vapor liquid solid growth of Si NWs from silane. c) phase diagram of Au-Si and Au-Ge systems, with eutectic points indicated. Adapted from [24].

The growth process comprises the following steps.

- A crystalline substrate exhibiting a specific plane Silicon in this work is covered with

metallic nanoparticles gold in this work able to form a eutectic alloy with the

substrate when heated and to catalyze CVD precursor decomposition reaction. These

nanoparticles (NPs) are denominated seeds and thus the process consisting in the

deposition of NP deposition on the substrate is the seeding method.

- The substrate is loaded into a CVD reactor and heated up above the eutectic point of the metal-substrate, forming liquid alloy droplets. In this work this temperature corresponds to that of the Au-Si eutectic point, namely 363 °C (Fig. 10c).

- The substrate within the CVD reactor is exposed to precursor gases (SiH<sub>4</sub>/GeH<sub>4</sub> in this work). The conditions of the CVD process temperature, pressure and flows are set

- so that the reaction of decomposition of precursor gases takes place only on the liquid eutectic NPs, which act as catalysts for such reaction.

- The local decomposition of precursors leads to the deposition of the material of interest into the eutectic droplet. In this work SiH<sub>4</sub> and GeH<sub>4</sub> decompose in Si, Ge and H<sub>2</sub> on the surface of the alloy (Eq. 19 and Eq. 20), leading to Si/Ge dissolution within the latter. The reaction byproducts H<sub>2</sub> in this work desorb and flow away.

$$SiH_4 \rightarrow Si + 2H_2$$

Eq. 19

$$GeH_4 \rightarrow Ge + 2H_2$$

Eq. 20

- The concentration of the deposited material is increased within the eutectic droplet, until a critical supersaturation point is reached. At this point the material begins its solid precipitation in the most energetically favorable surface in order to do so, namely, the underlying substrate. In this work this means that the Si/Ge atoms dissolved in the Au-Si eutectic droplet precipitate onto the underlying Si substrate exposing the <111> crystal plane.

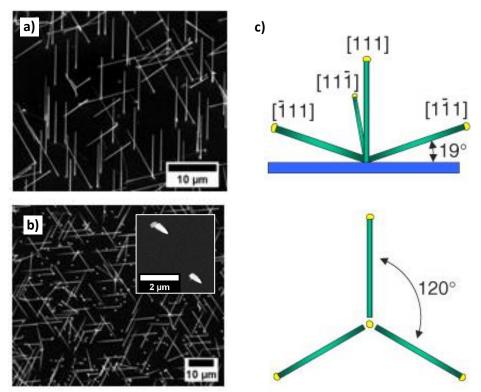

- CVD conditions can be chosen carefully so that an ordered enough process takes place, allowing the atoms to find a most favorable configuration for precipitation in positions following the underlying crystalline structure. That is, a substrate-epitaxial deposition can be attained, provided that the deposited material has the ability to grow in the same crystal structure. This is the case of Si/Ge/Si-Ge, which share all the diamond crystal structure of the Si substrate. Thus NWs in this work grew in the <111> direction exposed by the Si substrate plane.

- As decomposition reaction goes on a steady state is attained, with continuous incorporation of the material at droplet surface, diffusion through the alloy to substrate, and subsequent precipitation onto the substrate. Since the solid precipitate formed at the interphase has a dimeter limited by the size of the eutectic droplet, this process leads to the growth of NWs, as shown in Fig. 10. Thus, NWs grow outwards from the substrate, where they form a base, with the catalyst droplet on top.

- During the process the material to be deposited passes from a Vapour phase (carried in the gas precursor), through a Liquid phase (within the eutectic droplet) to a Solid phase (in the precipitated NW), hence the name of the VLS growth mechanism.

Rather than a single precursor, various precursors can be injected in the reactor during the CVD-VLS process in order to achieve different compositions and impurity doping in semiconductor nanowires. In this work diborane ( $B_2H_6$ ) was injected altogether with  $SiH_4$  and or  $GeH_4$  in order to obtain boron doped Si/Si-Ge NWs.

Auxiliary gases non-directly involved in the VLS mechanism may be added as well in order to settle necessary conditions for NW growth. In this work these were hydrogen (H<sub>2</sub>, which served as gas carrier and for dilution of precursor gases) and hydrochloric acid HCl (which helped avoiding catalyst migration and direct Vapour solid deposition in WN walls as will be discussed as follows and in Chapter 3).

VLS mechanism thus allows growing NWs whose diameter and areal density (NWs/ $\mu m^2$ ) controlled by seed NP diameter and density, and whose length is controlled by exposure time

to precursor gases during the CVD process – referred as growth time in this work. Composition and doping can be tailored as well by controlling the amounts of precursors and auxiliary gases injected during the CVD-VLS growth. All resultant morphology, composition and characteristics of the NWs are as well influenced by temperature and pressure, which are also controlling parameters, mostly influent in growth rate and aligned growth.

The controlling mechanisms listed herein were idealized in the sake of clarity. Several issues deviate the real scenario from a mere control of morphology based on growth time and seed size [25]. These are briefly reported herein and will be discussed thoroughly at Section 3.3.

For one, smallest seeds do not nucleate to NWs, breaking the assumption that density of seeds equals density of. Moreover preferred growth direction of NWs is diameter dependent, leading to non-<111> epitaxial NWs for the smallest seeds. Also, eutectic droplet diameter – and thus resulting NW diameter – is always bigger than that of the solid seed, due to the incorporation of Si atoms to the pristine Au NP. The most important deviation from ideality is the migration of gold atoms from the catalyst droplet to the lateral faces of the NW and to surrounding substrate. The main consequences are the shrinking of the droplet, the deposition of a pSi/pSi-Ge layer over the surfaces where gold has migrated and, a tapered profile and limited length of the grown NWs (ref, section ). This effect is so important – especially in Si-Ge NWs – that needs to be controlled by the addition of auxiliary HCl gas to the precursor mixture, which blocks gold migration preventing thus its consequences.

In this growth Si/Si-Ge NWs were grown and integrated in MEMS by means of the CVD-VLS method using gold nanoparticles (Au NP) as seeds. However many other catalysts are compatible for CVD-VLS growth of Si/Ge/Si-Ge NWs (Ag, Al, In, Ga, Zn, Pt, Ni, and Fe to cite some examples, [25]. The choice of gold as catalyst material for integration of NWs in the planar micro-devices was already discussed in the previous works [3]. Briefly, the use of gold presents several advantages: i) allows selective seeding by galvanic displacement described in following section, very suitable for integration of NWs targeted device parts; ii) if needed, allows growing NWs at temperatures as low as the eutectic point of Au-Si at 363 °C, which is very low among the other metal candidates for CVD-VLS catalysis. iii) the high solubility of Si/Ge in Au-Si eutectic allows a fast growth in comparison to thermoelectrics. iv) differently from Al – which up to this point presents the same advantages as Si for CVD-VLS catalysis – Au is extremely stable in ambient conditions, allowing to work at ambient conditions without the risk of oxidation – which is guaranteed for Al NPs unless controlled atmosphere is used, limiting their manageability.

Differently from the work started by Diana et all, which used liquid SiCl<sub>4</sub> as a Si precursor, silane (SiH<sub>4</sub>) and germane (GeH<sub>4</sub>) are used herein. These two gaseous precursors, diluted in hydrogen are much more user friendly that the former SiCl<sub>4</sub> which required a bubbler in order to deliver the gas to the CVD reactor. Moreover the use of silane allows reducing CVD-VLs growth temperature to 600 °C with respect to the 850 °C needed for decomposition and NW growth when SiCl4 is used. Thus the CVD-VLS growth of Si/Si-Ge NWs with these reactants and conditions yields a much more technology-friendly process paving the path for implementation in IC micro-fabrication lines.

Regarding the doping precursor a p-type dopant was used since the used micro-devices were p-type doped with boron, and so the use of n-type doped Si/Si-Ge NWs would lead to the formation of p-n junctions, which would implement a huge contact resistance in series with the NWs that would compromise device resistance. Moreover, recent studies suggest a negative surface charge in Si NWs exposed to air [26]. This leads to the formation of a depletion layer in n-type NWs, which reduces their carrier concentration and thus electrical conductivity. Among p-type dopant materials/precursors, boron doping with diborane ( $B_2H_6$ ) was used due to its extended use in clean rooms, which makes the NW based  $\mu$ TEG microfabrication process, once more, more prone to integration for mass production. Also, incorporation of boron to NWs by means of CVD-VLS mechanism has been demonstrated and studied by many groups [25], [27], [28].

#### 2.1.2.2. Seeding methods

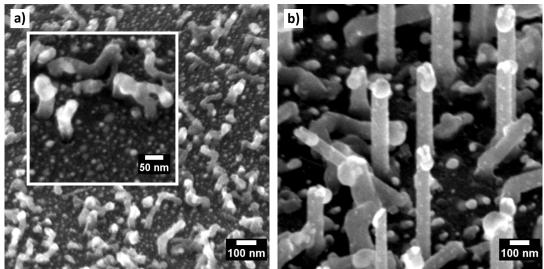

The methods employed for VLS seeding in this work were two, namely microemulsion galvanic displacement (galvanic displacement for short) and electrostatic colloid deposition (colloid deposition for short). While the first allows selective deposition of dense patterns of Au NPs on desired surfaces – targeted for NW array integration in micro-devices – the second allows sparse deposition Au colloids with fine control of the diameter – targeted for integration of *single* NWs in micro-structures for characterization purposes.

#### Microemulsion galvanic displacement

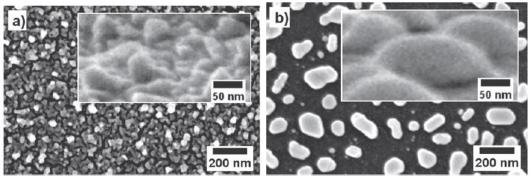

In a galvanic displacement process a redox reaction takes place so that part of a solid substrate is displaced to a liquid phase while a substance in the liquid phase is displaced to the substrate, depositing ono the latter as a solid [29], [30]. This process is often termed in other works as electroless deposition as it is compared to a conventional electrodeposition/electroplating process in which the same is attained by application of an electrical potential between solid and liquid phases [22].

In the microemulsion galvanic displacement employed herein silicon is partly removed from a surface while gold coming from a microemulsion is deposited onto it, by means of the following redox reactions:

$$Si_{(s)} + 6F_{(aq)}^{-} \rightarrow SiF_{6-(aq)}^{2-} + 2e^{-}$$

Eq. 21

$$Au_{(aq)}^{3+} + 3e^- \rightarrow Au_{(s)}$$

Eq. 22

where the subindexes refer to the phase in which the Au and Si species are included, namely aqueous phase of the microemulsion (aq) and solid (s). Aqueous phase of the microemulsion contains as well hydrofluoric acid HF, which is partly ionize to H<sup>+</sup> and F<sup>-</sup> for allowing reaction of Eq. 21. The fact that a microemulsion is used, with an organic phase not intervening in the reaction is for achieving Au nanoparticle - rather than thin film - deposition with size and density control, as explained following.

In microemulsion variant of galvanic displacement method, developed by Magagnin et al. in 2002 [29], a microemulsion comprising an aqueous and an organic phase is used, whose composition is shown in Table 3.

Table 3. Parameters for galvanic displacement microemulsion used in this work

| Phase            | Component                                   | Amount    |

|------------------|---------------------------------------------|-----------|

|                  | Hydrofluoric acid (HF)                      | 0.2 M     |

| Aqueous<br>phase | Gold containing salt (NaAuCl <sub>4</sub> ) | 0.01 M    |

|                  | Deionized water                             | (solvent) |

| Organia nhaca    | Surfactant (AOT)                            |           |

| Organic phase    | N-heptane                                   | (solvent) |

<sup>&</sup>lt;sup>a</sup>These parameters were fixed during the study

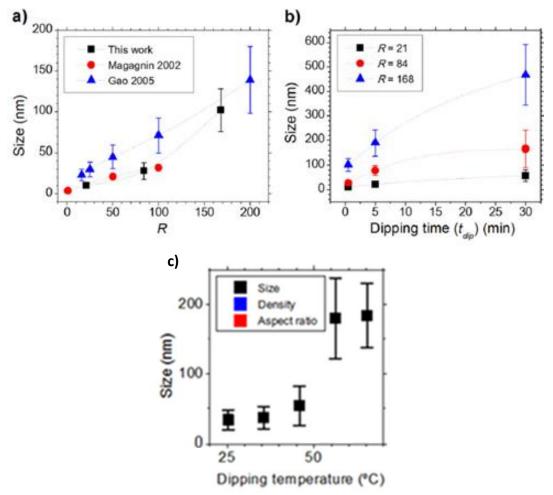

Different volumes of aqueous phase and organic phase are mixed leading to a reversed microemulsion of aqueous micelles coated by a surfactant layer, immersed in the organic phase, stable at room temperature. The size of these micelles is controlled by the amount of each phase added to the microemulsion. Specifically the radius of the micelle r is known to linearly vary with a microemulsion parameter R as:

$$r \text{ (in nm)} = 0.175 \cdot R + 1.5$$

where the unitless microemulsion parameter R is defined as:

$$R = \frac{[H_2O]}{[AOT]} = K \cdot \frac{V_{aq}}{V_{ora}}$$

Eq. 24

$V_{aq}$  and  $V_{org}$  are the volume of aqueous and organic phase added to the microemulsion respectively and K a constant depending on other parameters (concentrations shown in table XX and molecular weights) which is K=168 in our case.

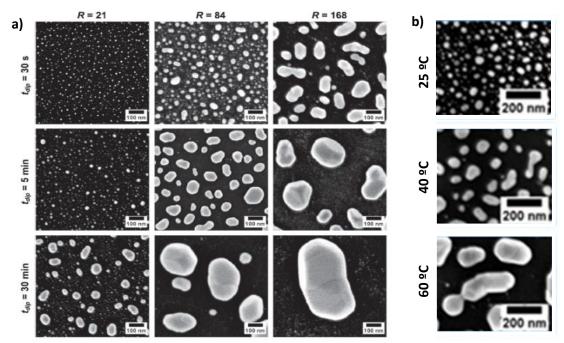

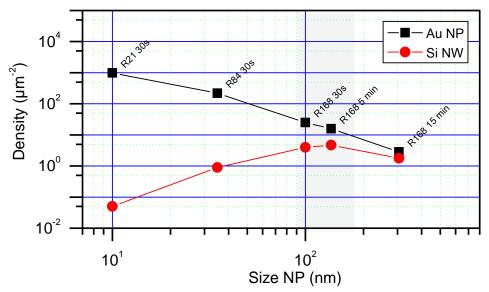

Thus, in this method micelles controlled size loaded with aqueous phase capable of performing a galvanic displacement reaction of Eq. 21 / Eq. 22 are prepared with this method. When a substrate containing silicon is exposed to this microemulsion, deposition of gold nanoparticles onto silicon takes place. The size and density of the resulting nanoparticles is controlled by the size of the micelles prepared this way, as was demonstrated by the authors and other works, which showed increasing NP size with increasing R value of the microemulsion [29], [31].

The reaction of Eq. 21 / Eq. 22 are only possible when convenient redox pairs are found in the solid/aqueous phase, namely when Nernst potentials such that the total reaction has a negative free energy. Thus, only specific substrates will yield to gold deposition, as the case of Si. When a Si substrate with partly passivated  $SiO_2/Si_3N_4$  surfaces were used in this process, Au NP deposition was observed only in Si exposed surfaces. This selective deposition supposes a great advantage for integration of NPs into devices. Specifically in this work, this allows a selective seeding of Au NPs in micro-device Si trenches, when the rest of Si surfaces are  $SiO_2/Si_3N_4$  passivated, which results in selective growth of NWs in targeted device parts, as demonstrated by [31], [32].

The microemulsion galvanic displacement employed herein (galvanic displacement for short from here on) allowed selective deposition of Au NPs on Si exposed surfaces with control of the particle size.

The exposition was attained by immersion (denominated dipping in this work) of the substrates into a solution with a controlled R parameter, during a controlled time (dip time or  $t_{dip}$ ) and at a controlled temperature (dipping temperature or  $T_{dip}$ ). The parameters determining the composition of each phase (Table 3) were fixed during all experiments. Typical total volumes of microemulsion for a 1 cm<sup>2</sup> chip were 10-25 ml. Magnetic stirring was employed during dipping in order to increase homogeneity, at 200-500 rpm with a 5 mm PTFE coated magnet.

Prior to the dipping, native oxide of the Si exposed surfaces was removed with hydrofluoric acid (HF) in order to facilitate deposition, since SiO2 should block the process. Later on it was found unnecessary as the HF present in aqueous phase did already so.

After the dipping, the substrates were rinsed with acetone and distilled water and dryad with pressurized nitrogen. Then, they were calcinated at 400 °C during 30 min in ambient air, in order to remove the possible remaining organic rests of the AOT surfactant of the organic phase. Table 4 summarizes the steps and conditions for the galvanic displacement seedings performed in this work.

**Table 4.** Microemulsion galvanic displacement conditions employed in this work

| Step                                                      | Conditions/parameters                                                                                                                                        |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Preparation of microemulsion                              | Mixing of different Vaq and Vorg prepared with compositions of Table 3, leading to a dipping parameter R = $168  V_{aq}/V_{org}$<br>Total volume of 10-25 ml |

| Native oxide removal from the substrate                   | 30 s in HF 5% weight Immersion in distilled water Drying with pressurized nitrogen (subsequent dipping process in the following 1 min)                       |

| Dipping (immersion) of the substrate in the microemulsion | R from 1 to 168  t <sub>dip</sub> from 0.5 to 30 min  T <sub>dip</sub> from 25 to 60 <sup>o</sup> C  Magnetic stirring at 200-500 rpm                        |

| Rinsing and drying of the sample                          | Immersion in acetone<br>Immersion distilled water<br>Drying with pressurized nitrogen                                                                        |

| Calcination of the sample                                 | Ramp from RT to 400 °C at a rate of 20 °C/min<br>Dwell of 30 min at 400 °C<br>Ramp from 400 °C to RT at a rate of 20 °C/min                                  |

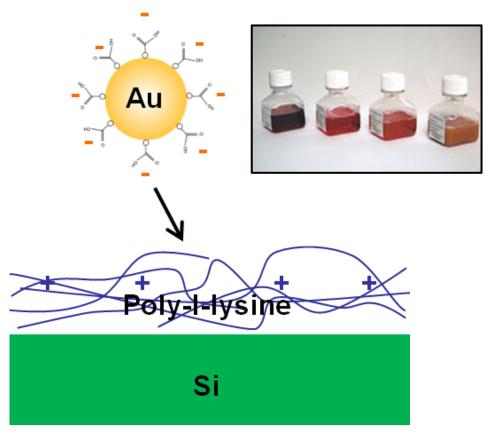

#### Electrostatic colloid deposition

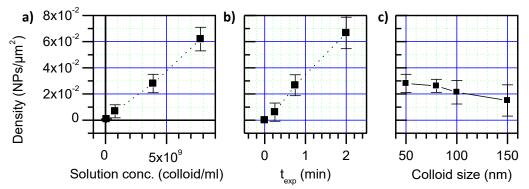

Briefly, this technique consists in exposing a substrate to a colloidal suspension previously coated with an auxiliary layer devoted to electrostatically attract the colloids. By doing this some colloids are deposited onto the substrate. Thus, the diameter of the deposited nanoparticles is exactly that of the colloids in the suspension, providing a means to finely control NW diameter, which is highly suitable for characterization. Moreover, resulting density

$(NPs/\mu m^2)$  is much lower than that obtained by galvanic displacement, which is useful for growth and integration of single NWs in characterization micro-structures introduced in Section 0.

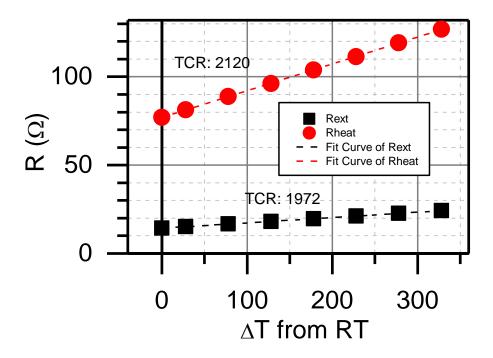

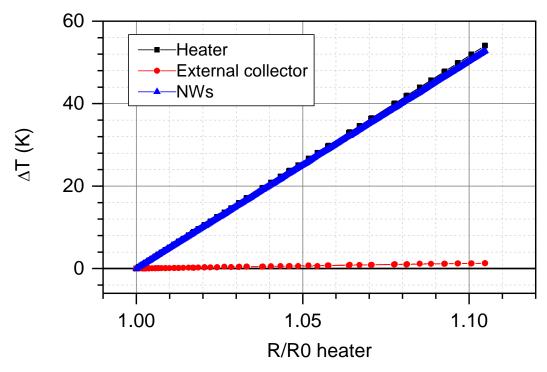

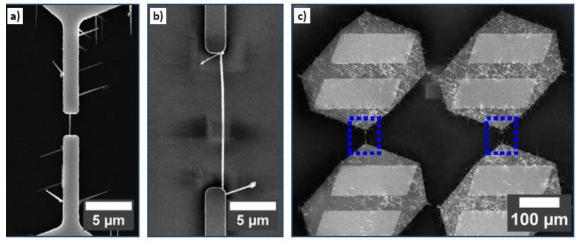

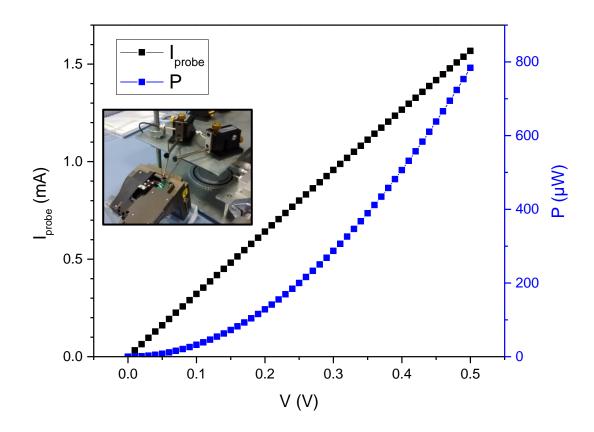

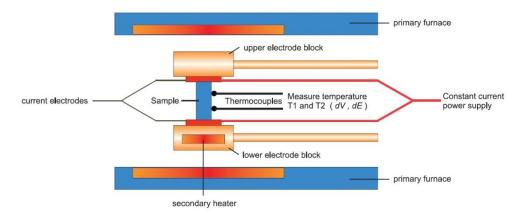

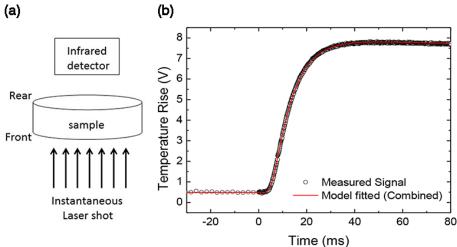

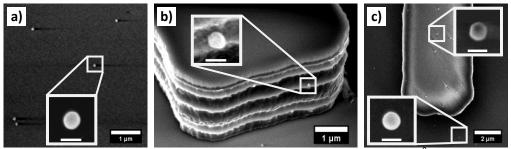

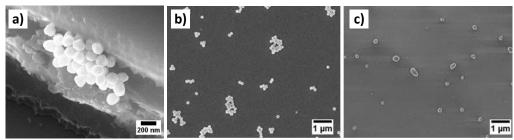

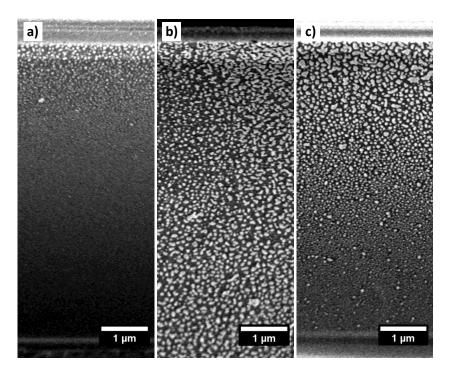

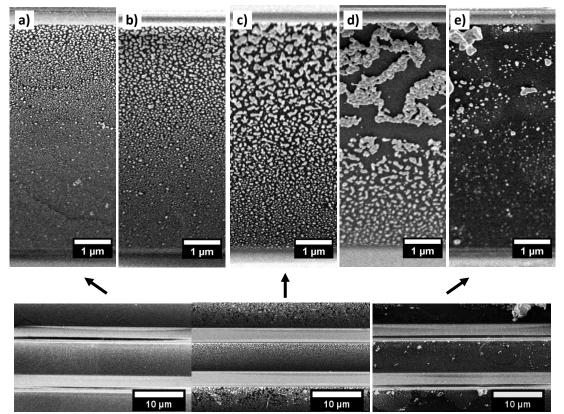

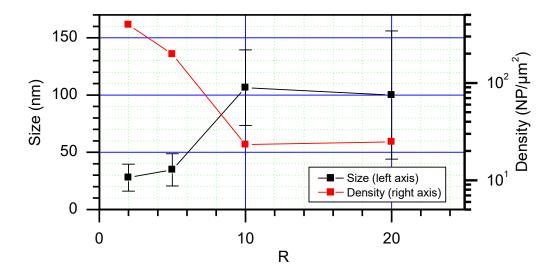

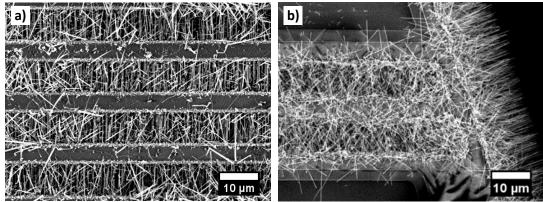

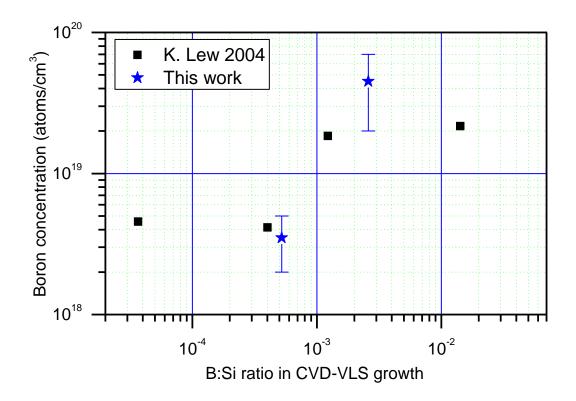

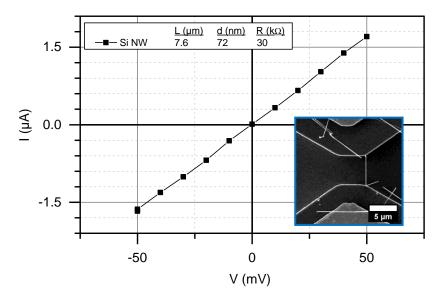

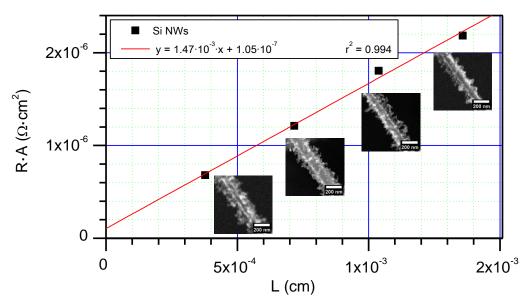

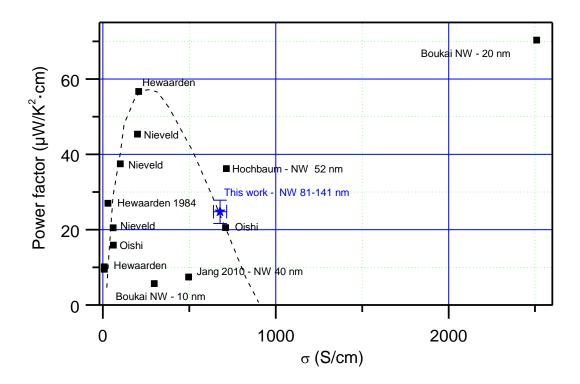

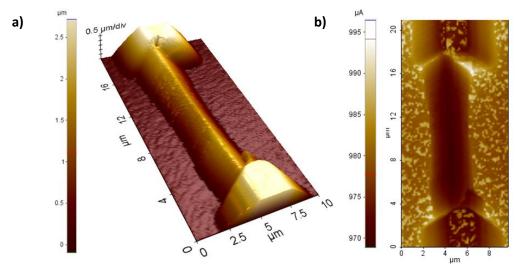

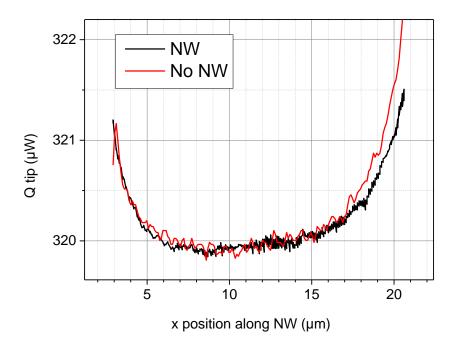

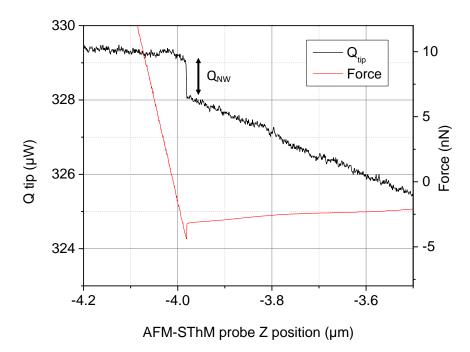

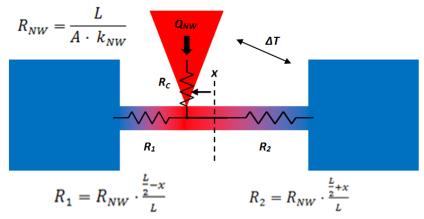

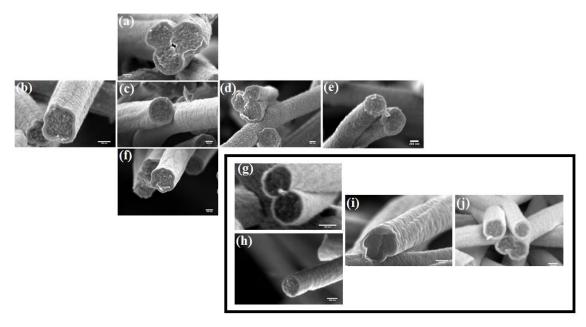

The approach followed herein is that of Hochbaum et al. [33], using aqueous citrate stabilized gold colloid suspensions and poly-l-lysine polymer in order to attain deposition on Si substrates. The process is schematized in Fig. 11 and described following.