# SiO<sub>2</sub>/Si 基板上へのグラフェン固相成長を用いた グラフェン電界効果トランジスタアレイの作製

Fabrication of Graphene Field Effect Transistor Arrays Using Solid-Phase Growth of Graphene on a SiO<sub>2</sub>/Si Substrate

水谷 孝 上席研究員

#### 概要

本報告では、SiO<sub>2</sub>/Si 基板上へのグラフェン固相成長を用いたグラフェン電界効果トランジスタアレイの作製について述べる。グラフェンを金属基板上ではなく SiO<sub>2</sub>/Si 基板上に成長により、転写が不要なグラフェン FET アレイの作製が可能となった。またグラフェンを島状に選択成長させることにより、素子間の電気的分離プロセスが不要となった。作製したデバイスはチャネル移動度 590cm<sup>2</sup>/Vs を有し、良好な電流—電圧特性を示した。

#### Abstract

In this study, graphene field effect transistor (FET) arrays were successfully fabricated, using solid-phase growth of graphene on a SiO<sub>2</sub>/Si substrate. Transfer-free fabrication was made possible by the fact the graphene was grown not on a metal catalyst film, but on an insulating SiO<sub>2</sub> substrate. Electrical isolation process was also eliminated by employing a patterned growth of graphene. The resultant device exhibited satisfactorily good current-voltage characteristics, with a mobility of 590 cm<sup>2</sup>/Vs.

*Index terms*: graphene, solid-phase growth, transfer-free fabrication, field effect transistor, FET

水谷 孝 Takashi Mizutani IEEE Fellow

E-mail: tmizu@nisri.jp

#### 1. はじめに

グラフェンは高いキャリア移動度[1]、小さい光吸収[2]、高い伝導度[3]をはじめとするすぐれた電気的、光学的、機械的および化学的性質を有することから[4]、次世代の高機能電界効果トランジスタ(FET)[5, 6]、超高速・高周波 FET[7,8]、フレキシブル透明電極[9, 10]、超高感度バイオセンサー[11]用材料として期待されている。

グラフェン研究の初期においては、単層/多層グラフェンは粘着テープを用いた機械的剥離により得られていた[12]。この手法は材料物性評価用の高品質グラフェンを得るのには適しているが、グラフェンの寸法や位置を制御することや大寸法グラフェンを得ることは困難であり、実用デバイスに適用するのは無理であった。この課題を解決する方法として、SiC 基板からの Si 蒸発[13-15]、酸化グラフェンの還元[16]、化学気相成膜(CVD)を用いたグラフェンの成長[17-19]などが検討された。

この中で触媒 Ni や Cu フィルム/基板上への CVD グラフェン成長は、グラフェンの大面積化が可能であることから広く検討された[20-23]。この CVD 成長グラフェンを FET に適用する場合、成長したグラフェンを絶縁性基板上に転写する必要があり、種々の転写技術が検討された[20, 22, 24-26]。 しかしながらこのような転写プロセスは比較的複雑であり、またクラックや皺が発生したりグラフェン表面が汚染されるなどの課題を有していた[27, 28]。従って FET の実用的な作製技術を開発するためには、グラフェンを絶縁性基板上に直接成長することが望ましい。

最近、グラフェン FET や集積回路には適用困難ではあるが、絶縁性 MgO ナノ粉末結晶上へのナノグラフェン直接成長が報告された[29]。一方、SiO $_2$ /Si 基板上に a-C/Ni/Au 3 層薄膜を成膜した後アニールを施すことにより、グラフェンが固相成長することが報告された[30]。われわれはこの技術を、グラフェンをソース/ドレイン電極とするカーボンナノチューブ(CNT)FET に適用し FET 動作を実証し、グラフェンを電極とする CNTFET は Au を電極とする CNTET よりも素子特性がすぐれていることを示した[31]。さらにコンタクト抵抗からグラフェンの層間抵抗を見積もることができた[32]。

本報告ではこれまでに得られた技術を発展させ、SiO2/Si 基板上へのグラフェン島状固相成長、およびこれを用いたグラフェン FET アレイの作製技術を検討した。本技術では、FET 作製歩留り低下の要因となるグラフェンの転写や素子の電気的分離エッチングが不要であり、高い素子歩留まりが期待され、将来のグラフェン FET 集積回路につながるものとして期待される。

#### 2. 実験および結果

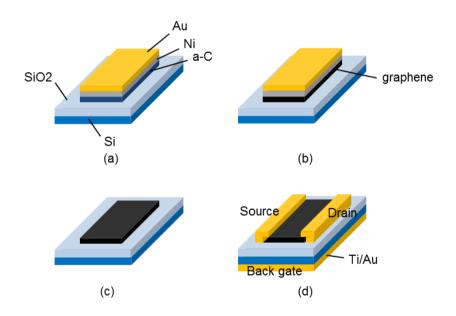

転送技術を用いないでグラフェン FET およびそのアレイを作製する技術の概要は以下のとおりである。すなわち、触媒金属のパターニングと、その触媒上への島状グラフェンの選択固相成長を用いるものである。本技術を用いたグラフェン FET アレイの作製フローを図 1 に示す。(a)まず最初に a-C(5 nm)/Ni(12.5 nm)/Au(30 nm) (a-C が下層) 3 層構造を、 $SiO_2/Si$  基板上の FET チャネル領域に、フォトリソグラフィーとそれに続く金属蒸着、リフトオフにより形成する。a-C はグラフェンの原料、Ni はグラフェン成長の触媒、Au は表面保護膜としての役割を果たす。(b)続いて固相グラフェン成長のための熱処理を  $800^{\circ}C$ 、15 分間、真空中( $\sim 10^{\circ}5$  Pa)の条件で行う。(c)Ni と Au を王水でエッチング除去してグラフェンのみを残す。(d)最後に Ti(10 nm)/Au(100 nm)電極をグラフェンチャネルのソース・ドレイン領域上および高濃度 Si バックゲート用基板裏面に形成する。ソース・ドレイン間距離は 20 µm である。

図1. グラフェン FET アレイの作製フロー

(a) a-C(5 nm)/Ni(12.5 nm)/Au(30 nm) (a-C が下層) 3層構造の形成、(b)800℃、15分の熱処理によるグラフェンの成長、(c)王水による Ni, Au のエッチング除去、(d) Ti(10 nm)/Au(100 nm)電極(ソース、ドレイン、裏面ゲート)の形成。

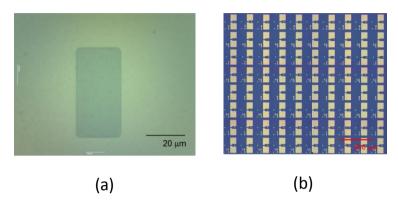

図 2(a)は上記選択固相成長法により形成した島状グラフェン $(20 \times 49 \ \mu m^2)$ の電子顕微鏡写真である。なお島状グラフェンの繰り返しは  $265 \ \mu m$  (縦方向)  $\times$   $285 \ \mu m$  (横方向) である。一様な薄膜が得られているのがわかる。グラフェン

の形成はラマン散乱測定におけるグラフェンに対応した 2D バンドピークを確認することにより、また層構造の形成は透過電子顕微鏡観察により確認した [31-32]。図 2(b)は作製したグラフェン FET アレイの顕微鏡写真である。

図2. (a)成長した矩形グラフェンおよび(b)グラフェン FET アレイの顕微鏡写真。

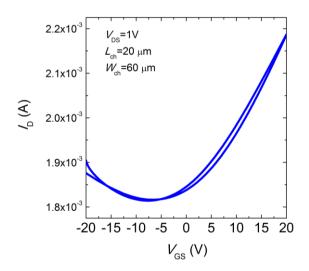

図3. グラフェン FET のゲート電流―ドレイン電圧特性

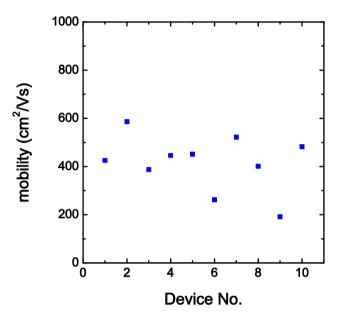

図3はドレイン電流一ゲート電圧転送特性の一例である。測定は空気中で行った。ドレイン電流は、ゲート電圧の正側・負側の両方向の変化に対して変調されており、両極性伝導が得られていることがわかる。空気中の測定にも関わらずヒステリシスが小さい。これはソース・ドレイン電極形成にメタルマスクを用いることにより、フォトレジスト等による汚染を防いだ効果が現れたと考えられる。グラフェン FET (10 個の)転送特性から求めたグラフェンチャネルの移動度を図4に示す。移動度は  $190\sim590~cm^2/Vs$  であった。これらの値は CVD

成長グラフェンの  $SiO_2/Si$  基板への転写を使って作製した FET と同じレベルである。ヒステリシスの小さい転送特性が得られたことを考えると、今回検討した選択固相成長を用いたグラフェン FET アレイの作製技術は、グラフェンの転写や素子間分離用エッチングが不要で、将来のグラフェン FET 集積回路作製のための有望技術であることを示している。

図4. グラフェン FET の転送特性から求めたキャリア移動度

### 3. まとめ

SiO2/Si 基板上にパターニングした a-c/Ni/Au 触媒を用いた島状グラフェンの選択固相成長とこの島状グラフェンをチャネルとするグラフェン FET アレイ作製技術を検討し、FET 動作を確認した。転送特性はヒステリシスが小さく、また転送特性から求めたキャリア移動度は 590cm²/Vs であった。この値はこれまでの熱 CVD 成長技術と同等の値である。今回有効性を確認した島状選択成長技術では、歩留り低下の要因となるグラフェンの転写や素子間分離エッチングが不要で高い FET 作製歩留りが期待され、将来のグラフェン FET 集積回路作製技術として有望と考えられる。

## 参考文献

- [1] K. Geim and K. S. Novoselov: Nat. Mater. 6, 183 (2007).

- [2] K. I. Bolotin, K. J. Sikes, Z. Jiang, M. Klima, G. Fudenberg, J. Hone, P.Kim, and H. L.

- Stormer: Solid State Commun. 146, 351 (2008).

- [3] R. R. Nair, P. Blake, A. N. Grigorenko, K. S. Novoselov, T. J. Booth, T.Stauber, N. M.

- R. Peres, and A. K. Geim: Science 320, 1308 (2008).

- [4] A. A. Balandin, S. Ghosh, W. Bao, I. Calizo, D. Teweldebrhan, F. Miao, and C. N. Lau: Nano Lett. 8, 902 (2008).

- [5] I. Meric, M. Y. Han, A. F. Young, B. Ozyilmaz, P. Kim, and K. L.Shepard: Nat. Nanotechnol. 3, 654 (2008).

- [6] D. Kondo, S. Sato, K. Yagi, N. Harada, M. Sato, M. Nihei, and N. Yokoyama: Appl. Phys. Express 3, 025102 (2010).

- [7] L. Liao, Y. Lin, M. Bao, R. Cheng, J. Bai, Y. Liu, Y. Qu, K. L. Wang, Y. Huang, and X. Duan: Nature **467**, 305 (2010).

- [8] Y. M. Lin, K. A. Jenkins, A. V. Garcia, J. P. Small, D. B. Farmer, and P.Avouris: Nano Lett. 9 (2009) 422.

- [9] K. S. Kim, Y. Zhao, H. Jang, S. Y. Lee, J. M. Kim, K. S. Kim, J. H. Ahn, P.Kim, J. Y. Choi, and B. H. Hong: Nature 457, 706 (2009).

- [10] X. Wang, L. Zhi, and K. Mu"llen: Nano Lett. 8, 323 (2008).

- [11] F. Schedin, A. K. Geim, S. V. Morozov, E. W. Hill, P. Blake, M. I.Katsnelson, and K. S. Novoselov: Nat. Mater. 6, 652 (2007).

- [12] K. S. Novoselov, D. Jiang, F. Schedin, T. J. Booth, V. V. Khotkevich, S. V.Morozov, and A. K. Geim: Proc. Natl. Acad. Sci. U.S.A. 102, 10451 (2005).

- [13] T. Ohta, A. Bostwick, T. Seyller, K. Horn, and E. Rotenberg: Science **313**, 951 (2006).

- [14] C. Berger, Z. Song, X. Li, X. Wu, N. Brown, C. Naud, D. Mayou, T. Li, J.

- Hass, A. N. Marchenkov, E. H. Conrad, P. N. First, and W. A. de Heer: Science 312, 1191 (2006).

- [15] H. Fukidome, Y. Miyamoto, H. Handa, E. Saito, and M. Suemitsu: Jpn. J.Appl. Phys. **49**, 01AH03 (2010).

- [16] C. G. Navarro, R. T. Weitz, A. M. Bittner, M. Scolari, A. Mews, M.Burghard, and K. Kern: Nano Lett. 7, 3499 (2007).

- [17] S. Y. Kwon, C. V. Ciobanu, V. Petrova, V. B. Shenoy, J. Bareno, V.Gambin, I. Petrov, and S. Kodambaka: Nano Lett. 9, 3985 (2009).

- [18] H. Ago, Y. Ito, N. Mizuta, K. Yoshida, B. Hu, C. M. Orofeo, M. Tsuji, K.Ikeda, and S. Mizuno: ACS Nano 4, 7407 (2010).

- [19] R. Negishi, H. Hirano, Y. Ohno, K. Maehashi, K. Matsumoto, and Y.Kobayashi: Thin Solid Films **519**, 6447 (2011).

- [20] A. Reina, X. Jia, J. Ho, D. Nezich, H. Son, V. Bulovic, M. S. Dresselhaus, and J.

- Kong: Nano Lett. 9, 30 (2009).

- [21] X. Li, W. Cai, L. Colombo, and R. S. Ruoff: Nano Lett. 9, 4268 (2009).

- [22] Q. Yu, J. Lian, S. Siriponglert, H. Li, Y. P. Chen, and S. S. Pei: Appl. Phys.Lett. 93, 113103 (2008).

- [23] L. Gao, J. R. Guest, and N. P. Guisinger: Nano Lett. 10, 3512 (2010).

- [24] J. W. Suk, A. Kitt, C. W. Magnuson, Y. Hao, S. Ahmed, J. An, A. K. Swan, B. B. Goldberg, R. S. Ruoff, ACS Nano 5, 6916 (2011).

- [25] J. Song, F. Y. Kam, R. Q. Png, W. L. Seah, J. M. Zhuo, G. K. Lim, P. K. H. Ho, L. L. Chua, *Nature* Nanotechnology 8, 356 (2013).

- [26] Y. Ren, C. Zhu, W. Cai, H. Li, Y. Hao, Y. Wu, S. Chen, Q. Wu, R. D. Piner, R. S. Ruoff, NANO: Brief Reports and Reviews 7, 1150001 (2012).

- [27] A. Srivastava, C. Galande, L. Ci, L. Song, C.Rai, D. Jariwala, K. F. Kelly, and P. M. Ajayan: Chem. Mater. 22, 3457 (2010).

- [28] K. Xu, P. Cao, and J. R. Heath: Nano Lett. 9, 4446 (2009).

- [29] M. H. Ru'mmeli, A. Bachmatiuk, A. Scott, F. Bo'rrnert, J. H. Warner, V.Hoffman, J.-H. Lin, G. Cuniberti, and B. Bu'chner: ACS Nano 4, 4206 (2010).

- [30] Y. Chai, A. Hazeghi, K. Takei, H.-Y. Chen, P. C. H. Chan, A. Javey, and H.-S. P. Wang, IEEE. Trans. Electron Devices **59**, 12 (2012).

- [31] M. Tamaoki, S. Kishimoto, Y. Ohno, and T. Mizutani, Appl. Phys. Lett. **101**, 033101 (2012).

- [32] M. Tamaoki, S. Kishimoto, Y. Ohno, and T. Mizutani, Appl. Phys. Lett. **103**, 033120 (2013).